PipelineC

@pipelinec.bsky.social

PipelineC Hardware Description Language

An easy to understand hardware description language with a powerful autopipelining compiler and growing set of real life design inspired features.

github.com/JulianKemmerer/PipelineC

https://discord.gg/Aupm3DDrK2

An easy to understand hardware description language with a powerful autopipelining compiler and growing set of real life design inspired features.

github.com/JulianKemmerer/PipelineC

https://discord.gg/Aupm3DDrK2

Pinned

PipelineC

@pipelinec.bsky.social

· Nov 17

Sphery vs. Shapes

YouTube video by Victor Suarez Rovere

youtu.be

You Bluesky folks seen this awesome work?

First raytraced game thats not software? 1080p realtime, interactive, fixed+float point, 3D vector math, no CPU, no instructions, autopipelined in #FPGA!

#raytracing #graphics #hardware #gamedev #hdl #verilog #vhdl #eda

youtu.be/hn3sr3VMJQU

First raytraced game thats not software? 1080p realtime, interactive, fixed+float point, 3D vector math, no CPU, no instructions, autopipelined in #FPGA!

#raytracing #graphics #hardware #gamedev #hdl #verilog #vhdl #eda

youtu.be/hn3sr3VMJQU

"How do FPGAs execute blocking assignments in one clock cycle?"

Is the perfect question to frame common learning curve hurdles that folks need to get over when learning HDL.

www.reddit.com/r/FPGA/comme...

#fpga #hardware #verilog #vhdl #hdl #rtl #hls #asic #eda

Is the perfect question to frame common learning curve hurdles that folks need to get over when learning HDL.

www.reddit.com/r/FPGA/comme...

#fpga #hardware #verilog #vhdl #hdl #rtl #hls #asic #eda

Software, FPGA Execution, a PipelineC response

www.reddit.com

August 7, 2025 at 9:37 PM

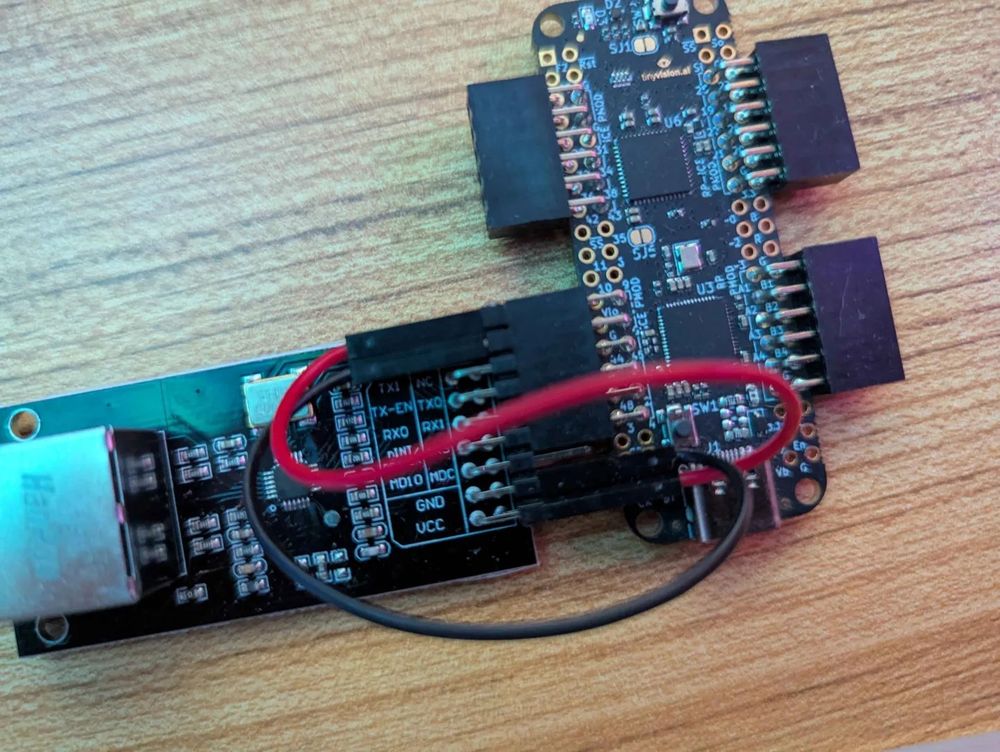

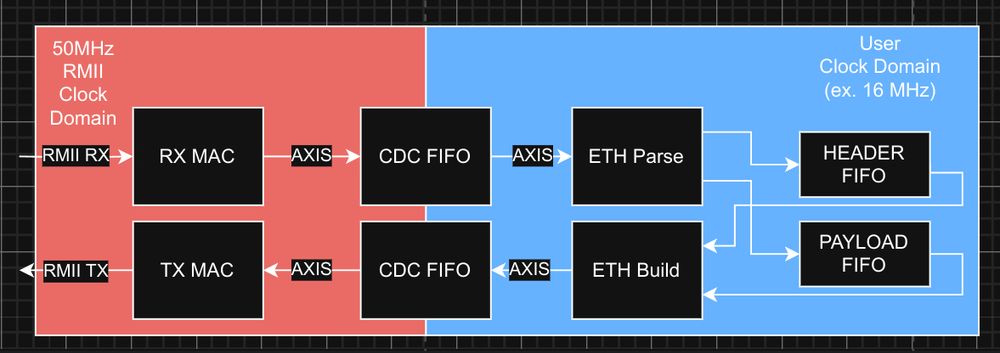

How to send a struct from one dev board to another? A PipelineC Story

#hdl #hls #RTL #fpga #ethernet #i2s #hardware

www.reddit.com/r/FPGA/comme...

#hdl #hls #RTL #fpga #ethernet #i2s #hardware

www.reddit.com/r/FPGA/comme...

From the FPGA community on Reddit: How to send a struct from one dev board to another?

Explore this post and more from the FPGA community

www.reddit.com

July 24, 2025 at 9:24 PM

Reposted by PipelineC

implemented a xilinx virtual cable applet. this way you can connect vivado to glasgow and program any supported FPGA

glasgow-embedded.org/latest/apple...

glasgow-embedded.org/latest/apple...

jtag-xvc - Glasgow Interface ExplorerContentsMenuExpandLight modeDark modeAuto light/dark, in light modeAuto light/dark, in dark mode

glasgow-embedded.org

May 22, 2025 at 5:51 AM

implemented a xilinx virtual cable applet. this way you can connect vivado to glasgow and program any supported FPGA

glasgow-embedded.org/latest/apple...

glasgow-embedded.org/latest/apple...

Reposted by PipelineC

#FPGA Congrats to Prof. Jason Cong, for Chuck Thacker Breakthrough in Computing Award, recognized for "fundamental contributions to the design and automation of field-programmable systems and customizable computing".

insidehpc.com/2025/04/jaso...

C-to-gates was a dream until Cong made it real.

insidehpc.com/2025/04/jaso...

C-to-gates was a dream until Cong made it real.

April 9, 2025 at 3:52 PM

#FPGA Congrats to Prof. Jason Cong, for Chuck Thacker Breakthrough in Computing Award, recognized for "fundamental contributions to the design and automation of field-programmable systems and customizable computing".

insidehpc.com/2025/04/jaso...

C-to-gates was a dream until Cong made it real.

insidehpc.com/2025/04/jaso...

C-to-gates was a dream until Cong made it real.

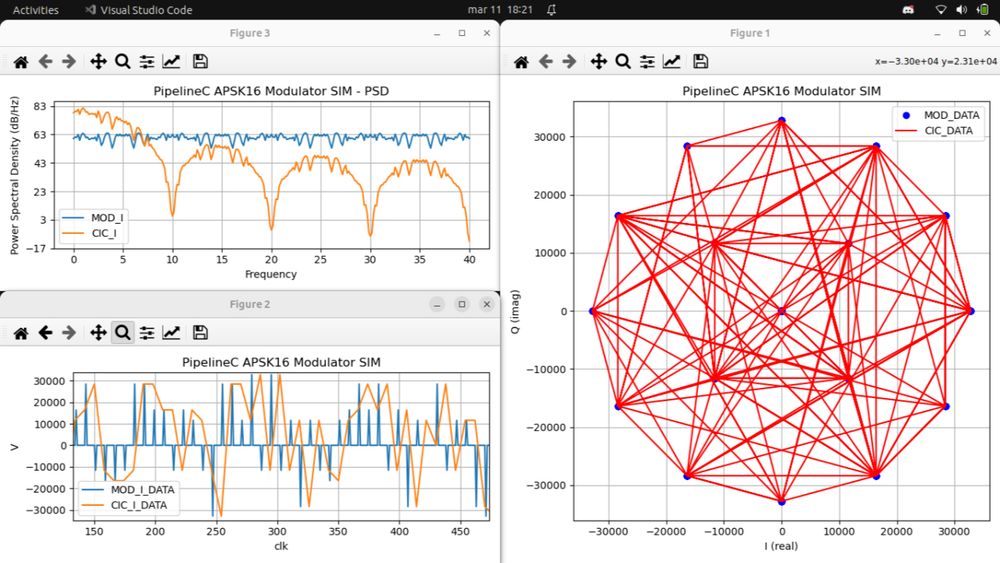

Check out @[email protected] 's very cool #16APSK #FPGA Modulator written in #PipelineC #HDL !

#dsp #sdr #rf #apsk #dac #deltasigma #space #qam #radio #hardware www.linkedin.com/pulse/16-aps...

#dsp #sdr #rf #apsk #dac #deltasigma #space #qam #radio #hardware www.linkedin.com/pulse/16-aps...

March 14, 2025 at 3:19 PM

Check out @[email protected] 's very cool #16APSK #FPGA Modulator written in #PipelineC #HDL !

#dsp #sdr #rf #apsk #dac #deltasigma #space #qam #radio #hardware www.linkedin.com/pulse/16-aps...

#dsp #sdr #rf #apsk #dac #deltasigma #space #qam #radio #hardware www.linkedin.com/pulse/16-aps...

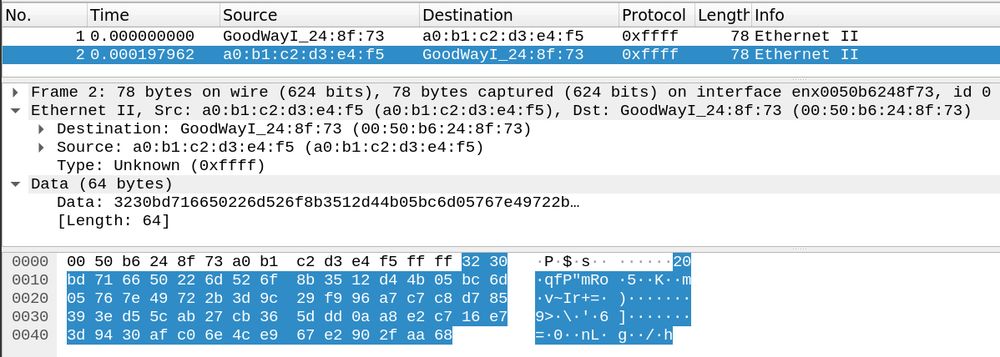

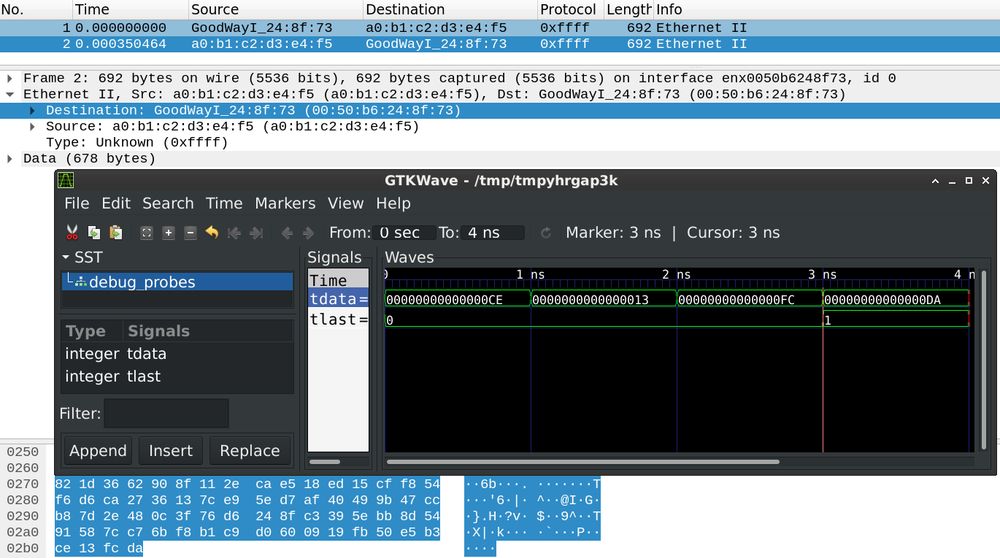

What can you do with reading arbitrary #FPGA registers out of your design over #UART? Capture time series data (last four #ethernet packet bytes), write a little #python script that launches #GTKWave, and you have a tiny homemade cross platform logic analyzer thing!

github.com/JulianKemmer...

github.com/JulianKemmer...

February 20, 2025 at 8:21 PM

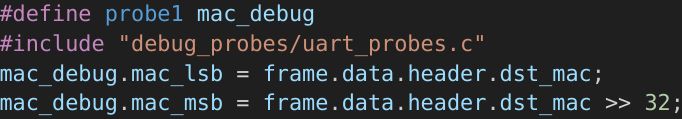

#hardware debugging and wanted to see some #ethernet MAC address registers down in my pico-ice #ice40 #fpga design. Don't want manufacturer specific ILAs. Don't want to route signals to top, external #debug equipment I don't have.

Just assign to #UART debug probe wire:

github.com/JulianKemmer...

Just assign to #UART debug probe wire:

github.com/JulianKemmer...

February 20, 2025 at 8:13 PM

Reposted by PipelineC

👋 Hi, I’m Max! Principal Engineer @ Intel & lead of ROHD, an open-source project making hardware design more fun & accessible.

Passionate about hardware, software, open source, and Dart. Also snowboarding, gaming, & new tech!

#introduction #opensource #hardware #FPGA #SoC #Dart #HDL #ROHD

Passionate about hardware, software, open source, and Dart. Also snowboarding, gaming, & new tech!

#introduction #opensource #hardware #FPGA #SoC #Dart #HDL #ROHD

February 2, 2025 at 7:01 PM

👋 Hi, I’m Max! Principal Engineer @ Intel & lead of ROHD, an open-source project making hardware design more fun & accessible.

Passionate about hardware, software, open source, and Dart. Also snowboarding, gaming, & new tech!

#introduction #opensource #hardware #FPGA #SoC #Dart #HDL #ROHD

Passionate about hardware, software, open source, and Dart. Also snowboarding, gaming, & new tech!

#introduction #opensource #hardware #FPGA #SoC #Dart #HDL #ROHD

Reposted by PipelineC

I taped out a variety of adders on open source silicon and Kogge-Stone adders were the fastest for all widths above 8 bits.

Yosys now has plugins to choose which topology you want! Read more here: www.zerotoasiccourse.com/post/instrum...

Yosys now has plugins to choose which topology you want! Read more here: www.zerotoasiccourse.com/post/instrum...

January 18, 2025 at 6:52 PM

I taped out a variety of adders on open source silicon and Kogge-Stone adders were the fastest for all widths above 8 bits.

Yosys now has plugins to choose which topology you want! Read more here: www.zerotoasiccourse.com/post/instrum...

Yosys now has plugins to choose which topology you want! Read more here: www.zerotoasiccourse.com/post/instrum...

Come learn some PipelineC #HDL basics featuring the pico-ice dev board from tinyVision.ai! It has a Lattice Semiconductor @latticesemi #ice40 #FPGA and @raspberrypi.com. This intro talk will cover #LED, #UART, and #VGA projects using OSS CAD Suite tools. #hardware #RTL #Verilog #VHDL #HLS

January 10, 2025 at 4:04 PM

Gifted a new #FPGA dev board this season? 🤓 PipelineC aims to make #hardware description easier for #embedded folks.

Check out the new getting start page. Happy to help you get going! #hdl #verilog #vhdl #hls

github.com/JulianKemmer...

Check out the new getting start page. Happy to help you get going! #hdl #verilog #vhdl #hls

github.com/JulianKemmer...

Dev Board Setup

A C-like hardware description language (HDL) adding high level synthesis(HLS)-like automatic pipelining as a language construct/compiler feature. - JulianKemmerer/PipelineC

github.com

December 26, 2024 at 4:19 PM

Part of why FPGAs are amazing is getting to be part of this hard 💪 hardware world while getting a relatively faster recompile and test cycle like software. I♥️#FPGA

It’s become a cliche, but hardware is hard! One reason why hardware is harder than software is that the time between revisions is often longer. We need to wait for new PCBs, or for components to be delivered. Or for more new PCBs after we realise we got it wrong!

December 15, 2024 at 5:29 AM

Part of why FPGAs are amazing is getting to be part of this hard 💪 hardware world while getting a relatively faster recompile and test cycle like software. I♥️#FPGA

Reposted by PipelineC

To help others progress, I’m going to award several Christmas test gear grants. If you’re interested, apply here: www.zerotoasiccourse.com/post/test-eq...

Test Equipment Grant

Apply for a grant to spend on test equipment

www.zerotoasiccourse.com

December 14, 2024 at 7:49 PM

To help others progress, I’m going to award several Christmas test gear grants. If you’re interested, apply here: www.zerotoasiccourse.com/post/test-eq...

Reposted by PipelineC

If you like thinking like: computers are the best thing humans have ever invented, ~= ASICs are practically pinnacle of science/innovation etc

then an FPGA on your desk at home

is this magical window into literally the coolest thing humans have ever done ~ computer architecture / digital design 🤓

then an FPGA on your desk at home

is this magical window into literally the coolest thing humans have ever done ~ computer architecture / digital design 🤓

just found out what an fpga is today and they sound like actual magic?? like you can just *program connections between gates like that*?????? actual insanity

December 4, 2024 at 5:21 PM

If you like thinking like: computers are the best thing humans have ever invented, ~= ASICs are practically pinnacle of science/innovation etc

then an FPGA on your desk at home

is this magical window into literally the coolest thing humans have ever done ~ computer architecture / digital design 🤓

then an FPGA on your desk at home

is this magical window into literally the coolest thing humans have ever done ~ computer architecture / digital design 🤓

Have been super pleased with the ice40 #FPGA and #raspberrypi board that pico-ice.tinyvision.ai sent me to experiment with. Many thanks and I look forward to putting together a talk for intro users getting started with #PipelineC and boards like the pico-ice 🤓 #HDL #Verilog #VHDL #hardware #embedded

pico-ice: Main Page

pico-ice.tinyvision.ai

November 30, 2024 at 7:20 PM

Have been super pleased with the ice40 #FPGA and #raspberrypi board that pico-ice.tinyvision.ai sent me to experiment with. Many thanks and I look forward to putting together a talk for intro users getting started with #PipelineC and boards like the pico-ice 🤓 #HDL #Verilog #VHDL #hardware #embedded

Reposted by PipelineC

I have a blog series on FPGA graphics: projectf.io/posts/fpga-g... with open-source designs for many dev boards including with Yosys. No ads or cookies.

Beginning FPGA Graphics

Welcome to Exploring FPGA Graphics. In this series, we learn about graphics at the hardware level and get a feel for the power of FPGAs. We’ll learn how screens work, play Pong, create starfields and ...

projectf.io

November 21, 2024 at 9:07 PM

I have a blog series on FPGA graphics: projectf.io/posts/fpga-g... with open-source designs for many dev boards including with Yosys. No ads or cookies.

😅😅😅😅😅😅😅😅😅 great post!

when i'm bored or distracted, i write blog posts about compilers, languages, and being a PhD student!

here is one of my favorites: rachit.pl/post/you-hav...

here is one of my favorites: rachit.pl/post/you-hav...

Dear Sir, You Have Built a Compiler | Rachit Nigam

rachit.pl

November 19, 2024 at 6:51 PM

😅😅😅😅😅😅😅😅😅 great post!

Reposted by PipelineC

since more people are joining bluesky, time for a re-intro!

i work on programming languages and compilers for hardware design and will be starting at MIT next year where i will lead the Foundations of Languages and Machines Lab (flame.csail.mit.edu).

if the ideas excites you, reach out to me!

i work on programming languages and compilers for hardware design and will be starting at MIT next year where i will lead the Foundations of Languages and Machines Lab (flame.csail.mit.edu).

if the ideas excites you, reach out to me!

FLAME Lab @ MIT

flame.csail.mit.edu

November 19, 2024 at 5:44 PM

since more people are joining bluesky, time for a re-intro!

i work on programming languages and compilers for hardware design and will be starting at MIT next year where i will lead the Foundations of Languages and Machines Lab (flame.csail.mit.edu).

if the ideas excites you, reach out to me!

i work on programming languages and compilers for hardware design and will be starting at MIT next year where i will lead the Foundations of Languages and Machines Lab (flame.csail.mit.edu).

if the ideas excites you, reach out to me!

Hve you tried an alternative to #verilog or #vhdl?

Not only does @thezoq2.bsky.social work on their own very cool Spade #rust inspired #HDL (and Surfer waveform viewer!) but they kindly have this awesome list to browse through too! 🤩 🤓 #fpga #rtl #asic #eda gitlab.com/TheZoq2/list...

Not only does @thezoq2.bsky.social work on their own very cool Spade #rust inspired #HDL (and Surfer waveform viewer!) but they kindly have this awesome list to browse through too! 🤩 🤓 #fpga #rtl #asic #eda gitlab.com/TheZoq2/list...

November 19, 2024 at 3:17 PM

Hve you tried an alternative to #verilog or #vhdl?

Not only does @thezoq2.bsky.social work on their own very cool Spade #rust inspired #HDL (and Surfer waveform viewer!) but they kindly have this awesome list to browse through too! 🤩 🤓 #fpga #rtl #asic #eda gitlab.com/TheZoq2/list...

Not only does @thezoq2.bsky.social work on their own very cool Spade #rust inspired #HDL (and Surfer waveform viewer!) but they kindly have this awesome list to browse through too! 🤩 🤓 #fpga #rtl #asic #eda gitlab.com/TheZoq2/list...

Reposted by PipelineC

the RTL debugger i'm working on can now show diagnostics in-line in the source code :D

November 15, 2024 at 4:45 PM

the RTL debugger i'm working on can now show diagnostics in-line in the source code :D

Reposted by PipelineC

PipelineC is a really neat approach to HDL design! A lot of PipelineC is valid C and can be "simulated" by just running it, but where it makes sense it also has hardware specific semantics that make it very different from high level synthesis

Oh, and the automatic pipelining is also very cool!

Oh, and the automatic pipelining is also very cool!

Enjoying dreaming of a world better than #Verilog or #VHDL? Come chat over on the #PipelineC Discord 🤓

Trying to make #HDL #RTL easier to write. Folks with #embedded experience, ever written #C for a #microcontroller with #hardware in mind, should feel right at home in #FPGA discord.gg/Aupm3DDrK2

Trying to make #HDL #RTL easier to write. Folks with #embedded experience, ever written #C for a #microcontroller with #hardware in mind, should feel right at home in #FPGA discord.gg/Aupm3DDrK2

November 19, 2024 at 10:01 AM

PipelineC is a really neat approach to HDL design! A lot of PipelineC is valid C and can be "simulated" by just running it, but where it makes sense it also has hardware specific semantics that make it very different from high level synthesis

Oh, and the automatic pipelining is also very cool!

Oh, and the automatic pipelining is also very cool!