PipelineC

@pipelinec.bsky.social

PipelineC Hardware Description Language

An easy to understand hardware description language with a powerful autopipelining compiler and growing set of real life design inspired features.

github.com/JulianKemmerer/PipelineC

https://discord.gg/Aupm3DDrK2

An easy to understand hardware description language with a powerful autopipelining compiler and growing set of real life design inspired features.

github.com/JulianKemmerer/PipelineC

https://discord.gg/Aupm3DDrK2

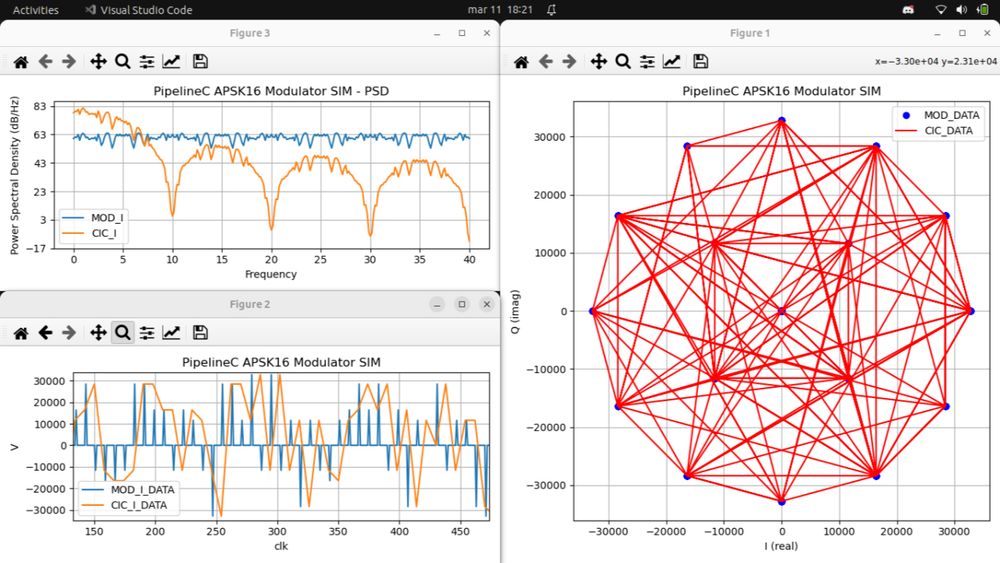

Check out @[email protected] 's very cool #16APSK #FPGA Modulator written in #PipelineC #HDL !

#dsp #sdr #rf #apsk #dac #deltasigma #space #qam #radio #hardware www.linkedin.com/pulse/16-aps...

#dsp #sdr #rf #apsk #dac #deltasigma #space #qam #radio #hardware www.linkedin.com/pulse/16-aps...

March 14, 2025 at 3:19 PM

Check out @[email protected] 's very cool #16APSK #FPGA Modulator written in #PipelineC #HDL !

#dsp #sdr #rf #apsk #dac #deltasigma #space #qam #radio #hardware www.linkedin.com/pulse/16-aps...

#dsp #sdr #rf #apsk #dac #deltasigma #space #qam #radio #hardware www.linkedin.com/pulse/16-aps...

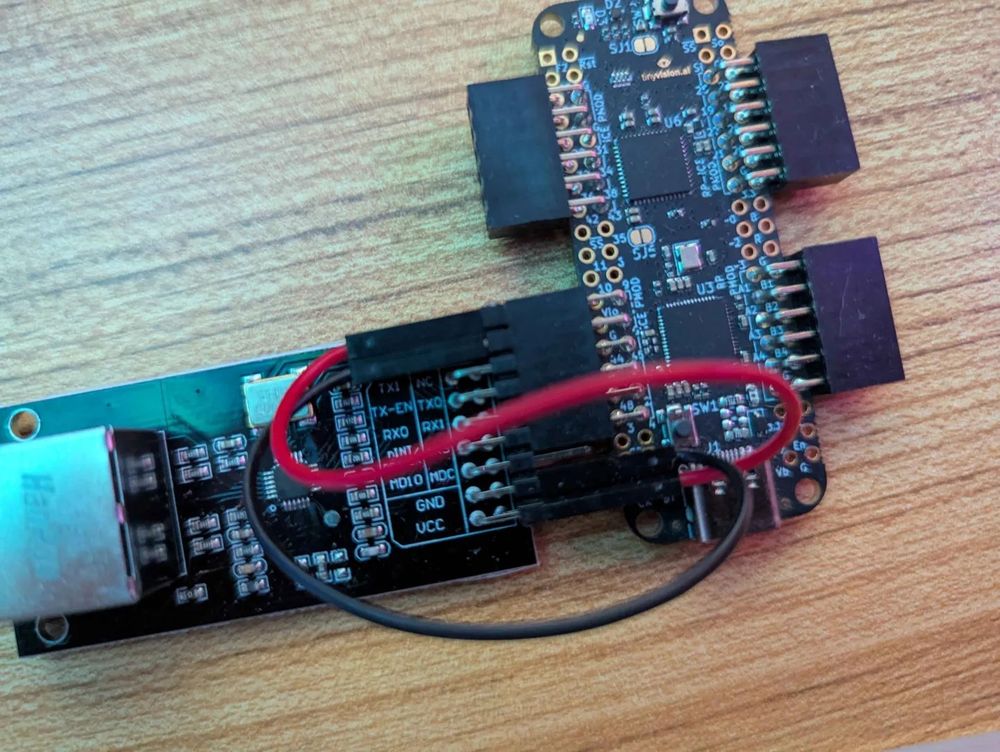

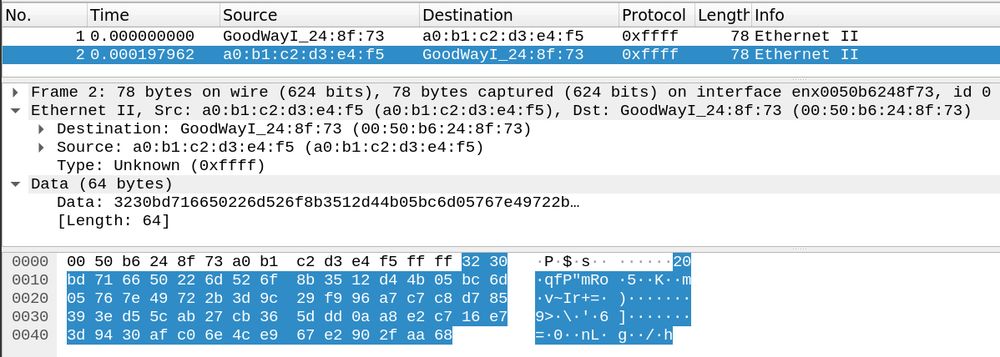

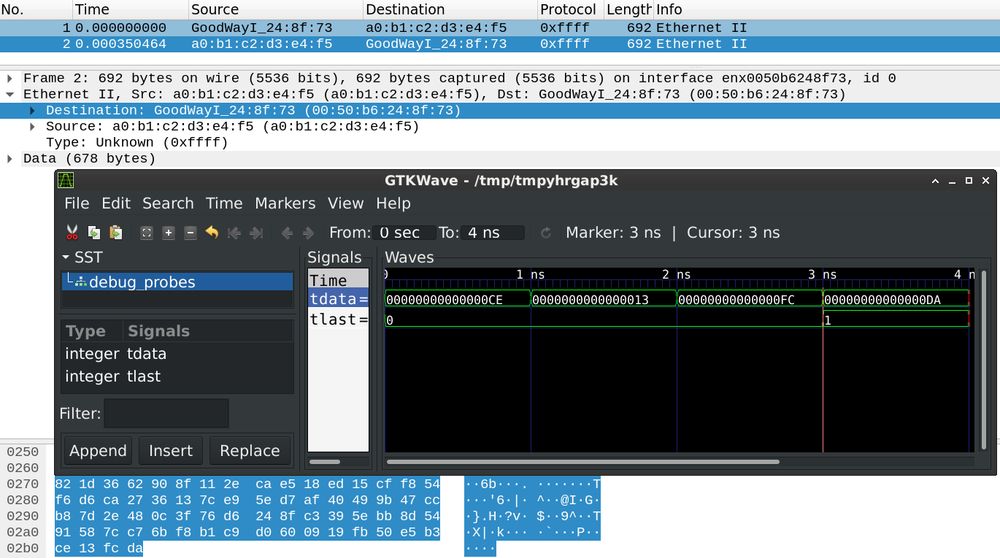

What can you do with reading arbitrary #FPGA registers out of your design over #UART? Capture time series data (last four #ethernet packet bytes), write a little #python script that launches #GTKWave, and you have a tiny homemade cross platform logic analyzer thing!

github.com/JulianKemmer...

github.com/JulianKemmer...

February 20, 2025 at 8:21 PM

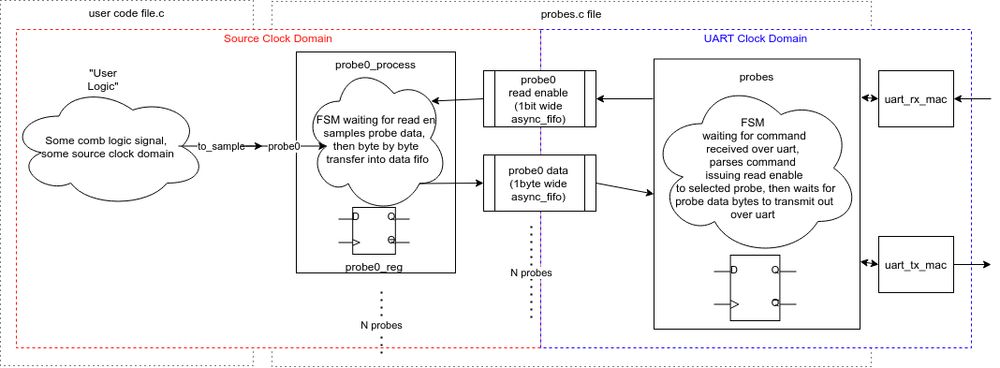

How does the hardware work? Probes can be in any clock domain and cdc to UART clock is handled for you with small FIFOs. Host PC control program read enable pulse causes hardware to respond over UART with the sample bytes from your debug probe. All included as a pipelinec library.

February 20, 2025 at 8:18 PM

How does the hardware work? Probes can be in any clock domain and cdc to UART clock is handled for you with small FIFOs. Host PC control program read enable pulse causes hardware to respond over UART with the sample bytes from your debug probe. All included as a pipelinec library.

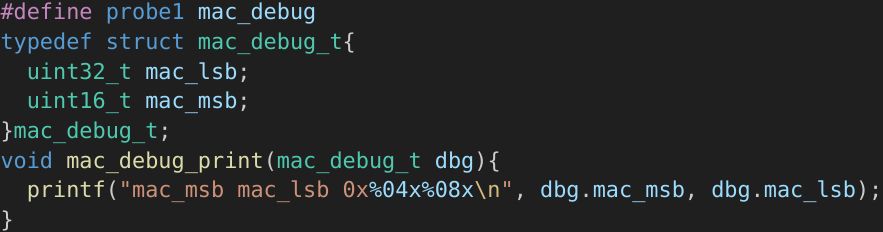

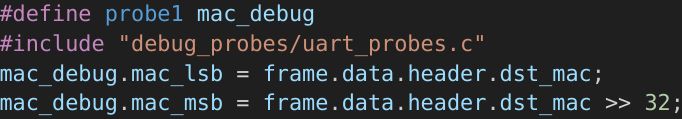

How do you configure this? You define a type and a method for printing the data to console. The struct type is shared between software C and hardware PipelineC. Upon receiving bytes for your probe they are converted to your struct type and printed as specified.

February 20, 2025 at 8:15 PM

How do you configure this? You define a type and a method for printing the data to console. The struct type is shared between software C and hardware PipelineC. Upon receiving bytes for your probe they are converted to your struct type and printed as specified.

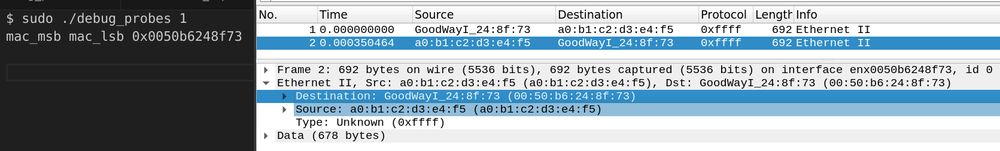

From there the bytes of probe data are shipped over UART to a host PC. A simple C program reading UART bytes displays your data:

February 20, 2025 at 8:15 PM

From there the bytes of probe data are shipped over UART to a host PC. A simple C program reading UART bytes displays your data:

#hardware debugging and wanted to see some #ethernet MAC address registers down in my pico-ice #ice40 #fpga design. Don't want manufacturer specific ILAs. Don't want to route signals to top, external #debug equipment I don't have.

Just assign to #UART debug probe wire:

github.com/JulianKemmer...

Just assign to #UART debug probe wire:

github.com/JulianKemmer...

February 20, 2025 at 8:13 PM

Come learn some PipelineC #HDL basics featuring the pico-ice dev board from tinyVision.ai! It has a Lattice Semiconductor @latticesemi #ice40 #FPGA and @raspberrypi.com. This intro talk will cover #LED, #UART, and #VGA projects using OSS CAD Suite tools. #hardware #RTL #Verilog #VHDL #HLS

January 10, 2025 at 4:04 PM

Hve you tried an alternative to #verilog or #vhdl?

Not only does @thezoq2.bsky.social work on their own very cool Spade #rust inspired #HDL (and Surfer waveform viewer!) but they kindly have this awesome list to browse through too! 🤩 🤓 #fpga #rtl #asic #eda gitlab.com/TheZoq2/list...

Not only does @thezoq2.bsky.social work on their own very cool Spade #rust inspired #HDL (and Surfer waveform viewer!) but they kindly have this awesome list to browse through too! 🤩 🤓 #fpga #rtl #asic #eda gitlab.com/TheZoq2/list...

November 19, 2024 at 3:17 PM

Hve you tried an alternative to #verilog or #vhdl?

Not only does @thezoq2.bsky.social work on their own very cool Spade #rust inspired #HDL (and Surfer waveform viewer!) but they kindly have this awesome list to browse through too! 🤩 🤓 #fpga #rtl #asic #eda gitlab.com/TheZoq2/list...

Not only does @thezoq2.bsky.social work on their own very cool Spade #rust inspired #HDL (and Surfer waveform viewer!) but they kindly have this awesome list to browse through too! 🤩 🤓 #fpga #rtl #asic #eda gitlab.com/TheZoq2/list...

Enjoying dreaming of a world better than #Verilog or #VHDL? Come chat over on the #PipelineC Discord 🤓

Trying to make #HDL #RTL easier to write. Folks with #embedded experience, ever written #C for a #microcontroller with #hardware in mind, should feel right at home in #FPGA discord.gg/Aupm3DDrK2

Trying to make #HDL #RTL easier to write. Folks with #embedded experience, ever written #C for a #microcontroller with #hardware in mind, should feel right at home in #FPGA discord.gg/Aupm3DDrK2

November 18, 2024 at 4:40 PM

Enjoying dreaming of a world better than #Verilog or #VHDL? Come chat over on the #PipelineC Discord 🤓

Trying to make #HDL #RTL easier to write. Folks with #embedded experience, ever written #C for a #microcontroller with #hardware in mind, should feel right at home in #FPGA discord.gg/Aupm3DDrK2

Trying to make #HDL #RTL easier to write. Folks with #embedded experience, ever written #C for a #microcontroller with #hardware in mind, should feel right at home in #FPGA discord.gg/Aupm3DDrK2

Last week spoke at the first annual Soft #RISCV Systems Workshop 🔥 about a #hardware #SoC in #FPGA made using #PipelineC for doing #DSP computing #FFT with custom hardware. Can see slides here (no recording): docs.google.com/presentation... #RISC-V #eda #asic #hls #rtl #hdl #verilog #vhdl

November 18, 2024 at 2:48 PM

'Shared Resource Buses': Multiple 'threads' of C function derived state machines share resources (memory, compute, etc) via AXI-like buses and arbitration. Reach out if you want to make something together! github.com/JulianKemmer... #rtl #hdl #hls #vhdl #verilog #asic #hardware #multithreaded #hpc

November 17, 2024 at 7:53 PM

'Shared Resource Buses': Multiple 'threads' of C function derived state machines share resources (memory, compute, etc) via AXI-like buses and arbitration. Reach out if you want to make something together! github.com/JulianKemmer... #rtl #hdl #hls #vhdl #verilog #asic #hardware #multithreaded #hpc

Use #PipelineC to listen to FM #radio with an #FPGA #SDR! Huge thanks to @[email protected] and @Darkknight512 for making first version a great learning experience. And @deepwavedigital for the fantastic hardware platform and workplace <3

#hardware #hdl #hls #asic

github.com/JulianKemmer...

#hardware #hdl #hls #asic

github.com/JulianKemmer...

November 17, 2024 at 7:51 PM

Use #PipelineC to listen to FM #radio with an #FPGA #SDR! Huge thanks to @[email protected] and @Darkknight512 for making first version a great learning experience. And @deepwavedigital for the fantastic hardware platform and workplace <3

#hardware #hdl #hls #asic

github.com/JulianKemmer...

#hardware #hdl #hls #asic

github.com/JulianKemmer...