PipelineC

@pipelinec.bsky.social

PipelineC Hardware Description Language

An easy to understand hardware description language with a powerful autopipelining compiler and growing set of real life design inspired features.

github.com/JulianKemmerer/PipelineC

https://discord.gg/Aupm3DDrK2

An easy to understand hardware description language with a powerful autopipelining compiler and growing set of real life design inspired features.

github.com/JulianKemmerer/PipelineC

https://discord.gg/Aupm3DDrK2

Yes that python running hardware has been all over this morning - super cool! Reminds me of some java/lisp machines from back in the day!

Also saw this Python to Digital Logic work today too - reminds me a smidge of pipelinec 🤓 repository.lincoln.ac.uk/articles/con...

Also saw this Python to Digital Logic work today too - reminds me a smidge of pipelinec 🤓 repository.lincoln.ac.uk/articles/con...

repository.lincoln.ac.uk

April 28, 2025 at 3:09 PM

Yes that python running hardware has been all over this morning - super cool! Reminds me of some java/lisp machines from back in the day!

Also saw this Python to Digital Logic work today too - reminds me a smidge of pipelinec 🤓 repository.lincoln.ac.uk/articles/con...

Also saw this Python to Digital Logic work today too - reminds me a smidge of pipelinec 🤓 repository.lincoln.ac.uk/articles/con...

Oh wow I didnt recall us speaking - but your post did remind me of that old desire for posix in hardware of some kind 🤓 Good to hear you are still around looking at cool things too!

April 28, 2025 at 3:07 PM

Oh wow I didnt recall us speaking - but your post did remind me of that old desire for posix in hardware of some kind 🤓 Good to hear you are still around looking at cool things too!

Will this (fpga+cpu+graphics) make it into a projectf tutorial somewhere? Seems like everyone wants to make their own GPU and this feels like a perfect intro 🤓

March 9, 2025 at 4:35 PM

Will this (fpga+cpu+graphics) make it into a projectf tutorial somewhere? Seems like everyone wants to make their own GPU and this feels like a perfect intro 🤓

yeah 'set the clock too high' build to evaluate fmax is something the pipelinec tool does as well. But be careful some tools, if given a large design with a goal too high they will give up early and you won't get representative fmax out.

March 9, 2025 at 4:27 PM

yeah 'set the clock too high' build to evaluate fmax is something the pipelinec tool does as well. But be careful some tools, if given a large design with a goal too high they will give up early and you won't get representative fmax out.

Id say its this reasoning that the tools don't tell you fmax. Most users have a target and just want to know if they made it there or not 🤷

March 9, 2025 at 4:26 PM

Id say its this reasoning that the tools don't tell you fmax. Most users have a target and just want to know if they made it there or not 🤷

It's a C like HDL. So gets you into describing hardware without needing to learn verilog sensitivity lists and blocking non blocking etc. So just hopefully easier. And then has some fancier compiler things it can do: ex. help you pipeline for high performance designs 🤙

March 5, 2025 at 9:48 PM

It's a C like HDL. So gets you into describing hardware without needing to learn verilog sensitivity lists and blocking non blocking etc. So just hopefully easier. And then has some fancier compiler things it can do: ex. help you pipeline for high performance designs 🤙

Happen to know some basic C? If you are in the mood to experiment with getting right to hardware design and past the annoying Verilog/VHDL learning curve - happy to chat about PipelineC 🤓

March 5, 2025 at 3:44 PM

Happen to know some basic C? If you are in the mood to experiment with getting right to hardware design and past the annoying Verilog/VHDL learning curve - happy to chat about PipelineC 🤓

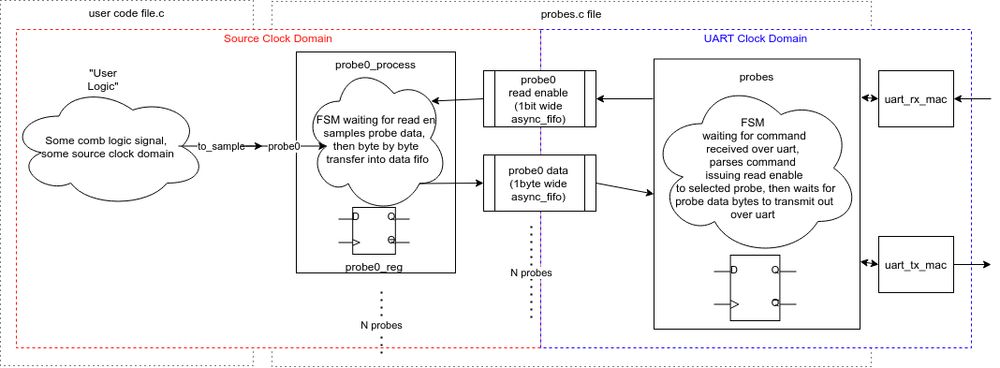

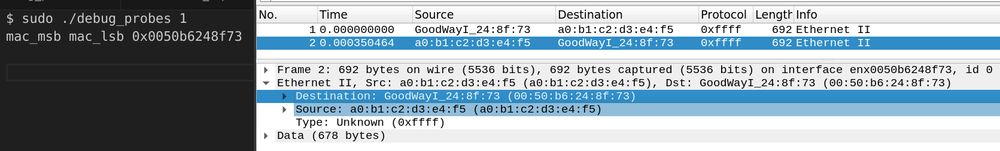

How does the hardware work? Probes can be in any clock domain and cdc to UART clock is handled for you with small FIFOs. Host PC control program read enable pulse causes hardware to respond over UART with the sample bytes from your debug probe. All included as a pipelinec library.

February 20, 2025 at 8:18 PM

How does the hardware work? Probes can be in any clock domain and cdc to UART clock is handled for you with small FIFOs. Host PC control program read enable pulse causes hardware to respond over UART with the sample bytes from your debug probe. All included as a pipelinec library.

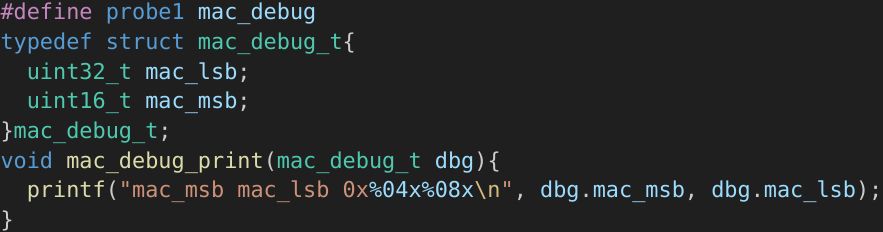

How do you configure this? You define a type and a method for printing the data to console. The struct type is shared between software C and hardware PipelineC. Upon receiving bytes for your probe they are converted to your struct type and printed as specified.

February 20, 2025 at 8:15 PM

How do you configure this? You define a type and a method for printing the data to console. The struct type is shared between software C and hardware PipelineC. Upon receiving bytes for your probe they are converted to your struct type and printed as specified.

From there the bytes of probe data are shipped over UART to a host PC. A simple C program reading UART bytes displays your data:

February 20, 2025 at 8:15 PM

From there the bytes of probe data are shipped over UART to a host PC. A simple C program reading UART bytes displays your data:

Learn PipelineC #HDL basics featuring the pico-ice dev board from tinyVision.ai! It has a Lattice Semiconductor @latticesemi #ice40 #FPGA and @Raspberrypi. This intro covers #LED, #UART, and #VGA projects using OSS CAD Suite tools. #hardware #RTL #Verilog #VHDL #HLS

www.youtube.com/watch?v=wWdv...

www.youtube.com/watch?v=wWdv...

Introduction to PipelineC

YouTube video by PipelineC

www.youtube.com

January 18, 2025 at 5:55 PM

Saturday Jan. 18th

12PM EST

via Watch2Gether:

w2g.tv/?r=tx4wy991roihexnj7g

(no account required)

Recording published after.

github.com/JulianKemmerer/PipelineC/wiki

pico-ice.tinyvision.ai

github.com/YosysHQ/oss-cad-suite-build

Fallback location is tinyVision.ai Discord: discord.gg/zzZZj57ZmZ

12PM EST

via Watch2Gether:

w2g.tv/?r=tx4wy991roihexnj7g

(no account required)

Recording published after.

github.com/JulianKemmerer/PipelineC/wiki

pico-ice.tinyvision.ai

github.com/YosysHQ/oss-cad-suite-build

Fallback location is tinyVision.ai Discord: discord.gg/zzZZj57ZmZ

Let's meet on Watch2Gether

Watch2Gether lets you watch videos with your friends, synchronized at the same time.

w2g.tv

January 10, 2025 at 4:05 PM

Saturday Jan. 18th

12PM EST

via Watch2Gether:

w2g.tv/?r=tx4wy991roihexnj7g

(no account required)

Recording published after.

github.com/JulianKemmerer/PipelineC/wiki

pico-ice.tinyvision.ai

github.com/YosysHQ/oss-cad-suite-build

Fallback location is tinyVision.ai Discord: discord.gg/zzZZj57ZmZ

12PM EST

via Watch2Gether:

w2g.tv/?r=tx4wy991roihexnj7g

(no account required)

Recording published after.

github.com/JulianKemmerer/PipelineC/wiki

pico-ice.tinyvision.ai

github.com/YosysHQ/oss-cad-suite-build

Fallback location is tinyVision.ai Discord: discord.gg/zzZZj57ZmZ