Greg

@gregdavill.bsky.social

ASIC/FPGA/PCB/FW engineer at ASTC 🧙♂️ (He/Him)

I also take macro photos of electronics

I also take macro photos of electronics

I'd forgotten that the ECP5-25F doesn't have all the I/O, and 4 or so pins that are on the 45/85F are N/C on the 25F. I just happened to use one of these for the ULPI interface. 🥲

Bodge wire to the rescue! Now we're enumerating again!

USB boot loader in gateware, takes up ~15% of the device

Bodge wire to the rescue! Now we're enumerating again!

USB boot loader in gateware, takes up ~15% of the device

September 2, 2025 at 12:30 PM

I'd forgotten that the ECP5-25F doesn't have all the I/O, and 4 or so pins that are on the 45/85F are N/C on the 25F. I just happened to use one of these for the ULPI interface. 🥲

Bodge wire to the rescue! Now we're enumerating again!

USB boot loader in gateware, takes up ~15% of the device

Bodge wire to the rescue! Now we're enumerating again!

USB boot loader in gateware, takes up ~15% of the device

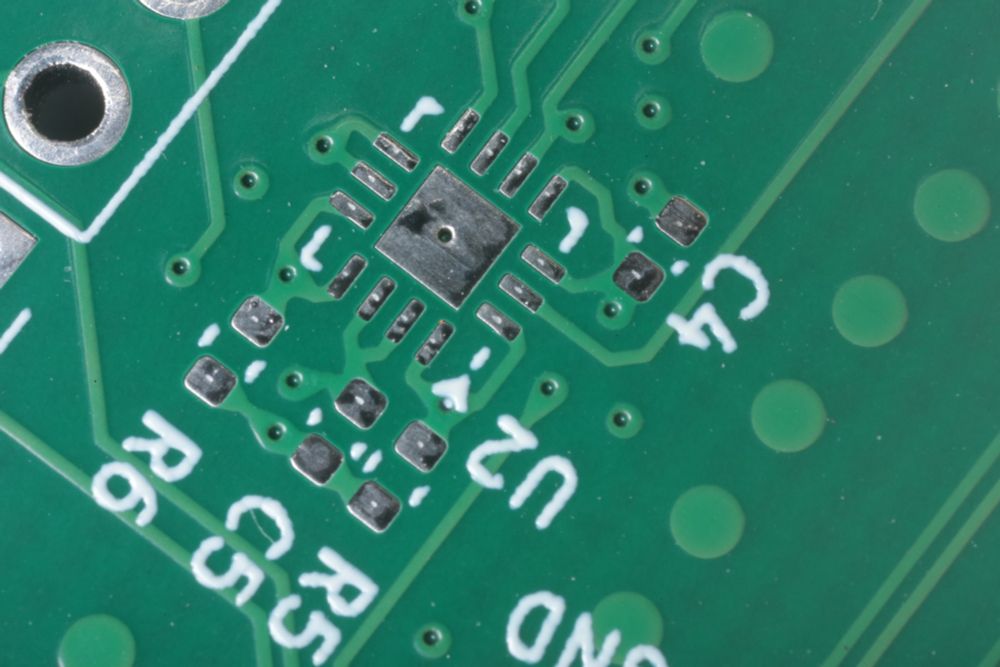

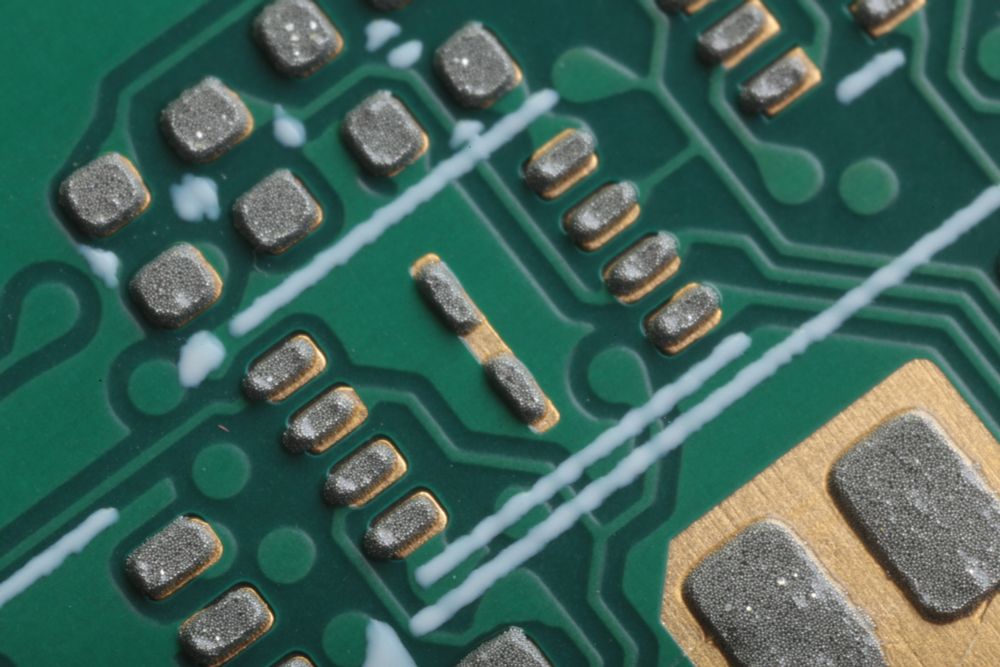

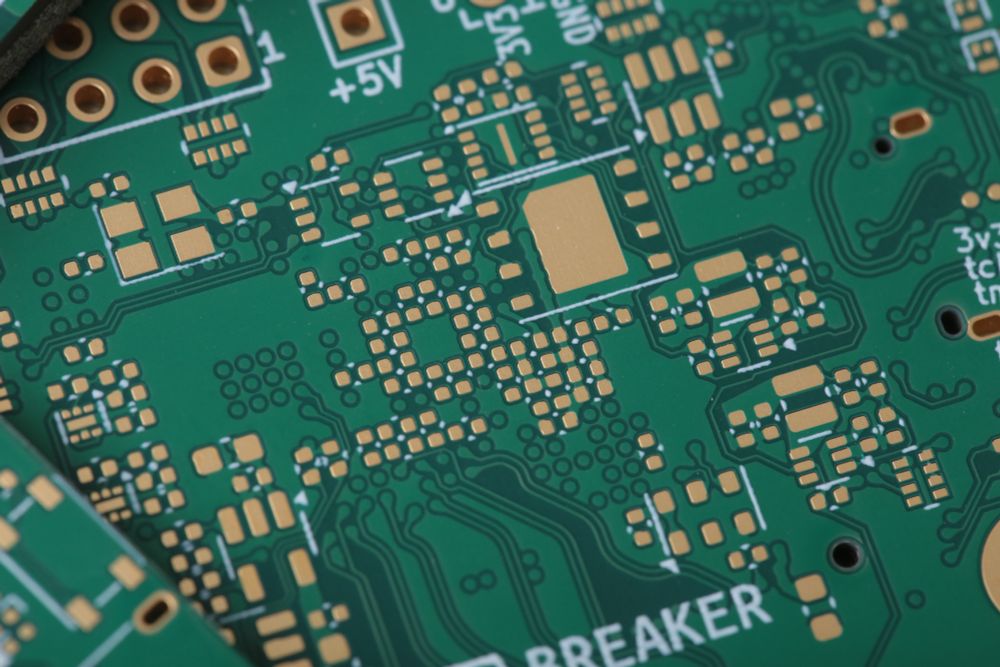

These two boards have the same BGA geometry defined in their gerbers. For some reason JLCs DFM adjustments have expanded all the "via in pad" connections.

Makes for an interesting visual effect.

Makes for an interesting visual effect.

September 1, 2025 at 12:55 PM

These two boards have the same BGA geometry defined in their gerbers. For some reason JLCs DFM adjustments have expanded all the "via in pad" connections.

Makes for an interesting visual effect.

Makes for an interesting visual effect.

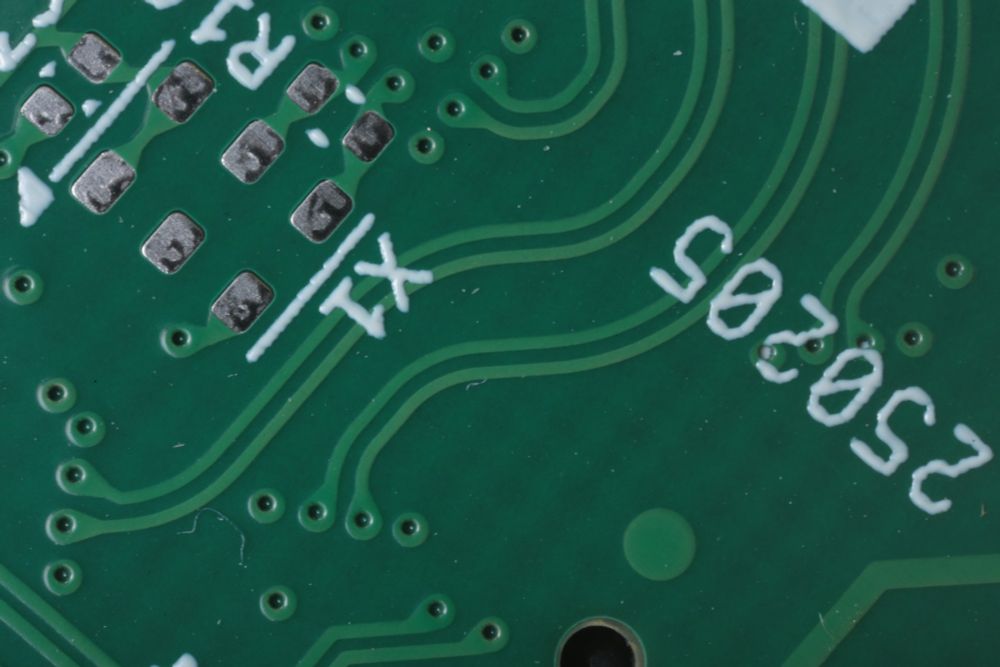

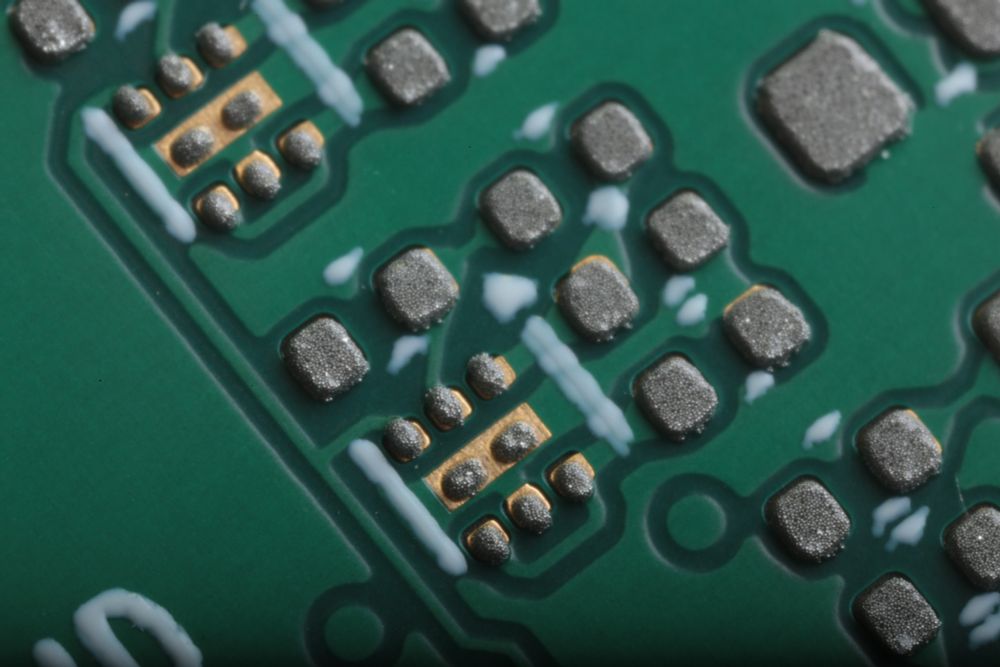

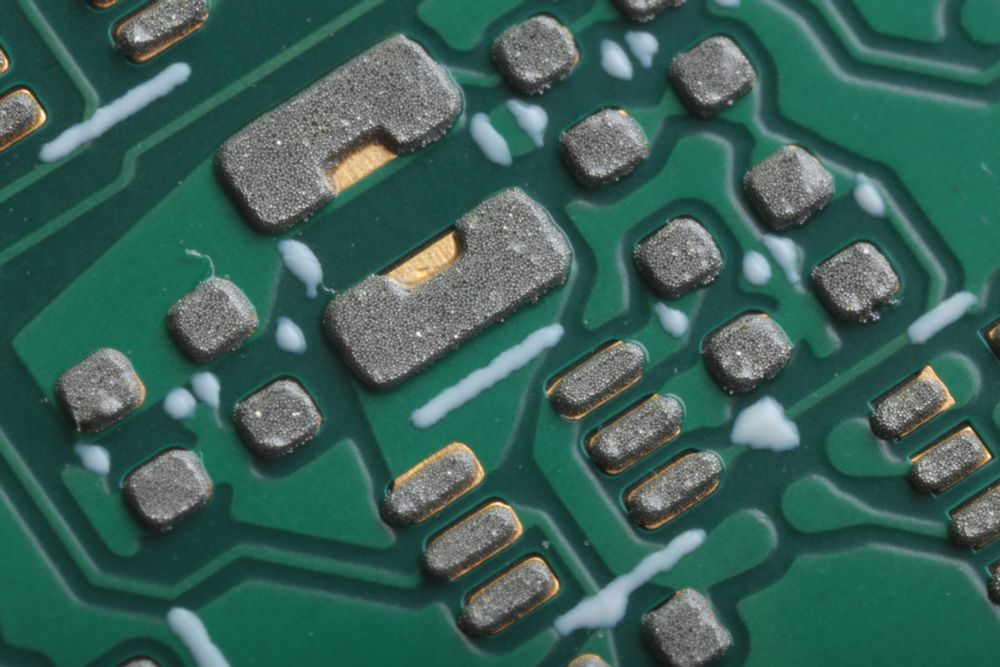

How's my solder paste application?

I think I missed some spots. 🫣

I think I missed some spots. 🫣

September 1, 2025 at 11:32 AM

How's my solder paste application?

I think I missed some spots. 🫣

I think I missed some spots. 🫣

FPGAs programming FPGAs 🐢

August 23, 2025 at 2:53 AM

FPGAs programming FPGAs 🐢

The bodge works!

A DFF in front of the ECP5's FPGA SPI configuration port before a mix leading to FLASH and PSRAM. Enabling an initial jump through FLASH where the clock frequency is bumped and QSPI entered.

This now fixes an issue violating the PSRAM's tCE<8us requirement.

A DFF in front of the ECP5's FPGA SPI configuration port before a mix leading to FLASH and PSRAM. Enabling an initial jump through FLASH where the clock frequency is bumped and QSPI entered.

This now fixes an issue violating the PSRAM's tCE<8us requirement.

August 17, 2025 at 10:41 AM

The bodge works!

A DFF in front of the ECP5's FPGA SPI configuration port before a mix leading to FLASH and PSRAM. Enabling an initial jump through FLASH where the clock frequency is bumped and QSPI entered.

This now fixes an issue violating the PSRAM's tCE<8us requirement.

A DFF in front of the ECP5's FPGA SPI configuration port before a mix leading to FLASH and PSRAM. Enabling an initial jump through FLASH where the clock frequency is bumped and QSPI entered.

This now fixes an issue violating the PSRAM's tCE<8us requirement.

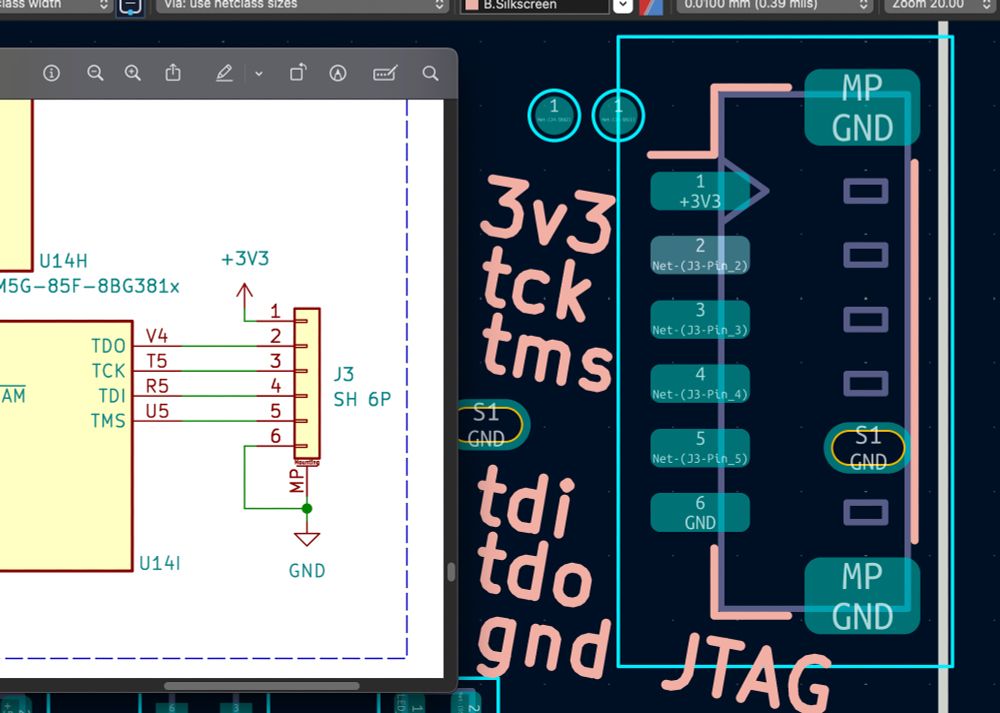

Plan vs. Execution

The messier the plan the cleaner the bodge looks in comparison. 😅

The messier the plan the cleaner the bodge looks in comparison. 😅

August 16, 2025 at 11:26 PM

Plan vs. Execution

The messier the plan the cleaner the bodge looks in comparison. 😅

The messier the plan the cleaner the bodge looks in comparison. 😅

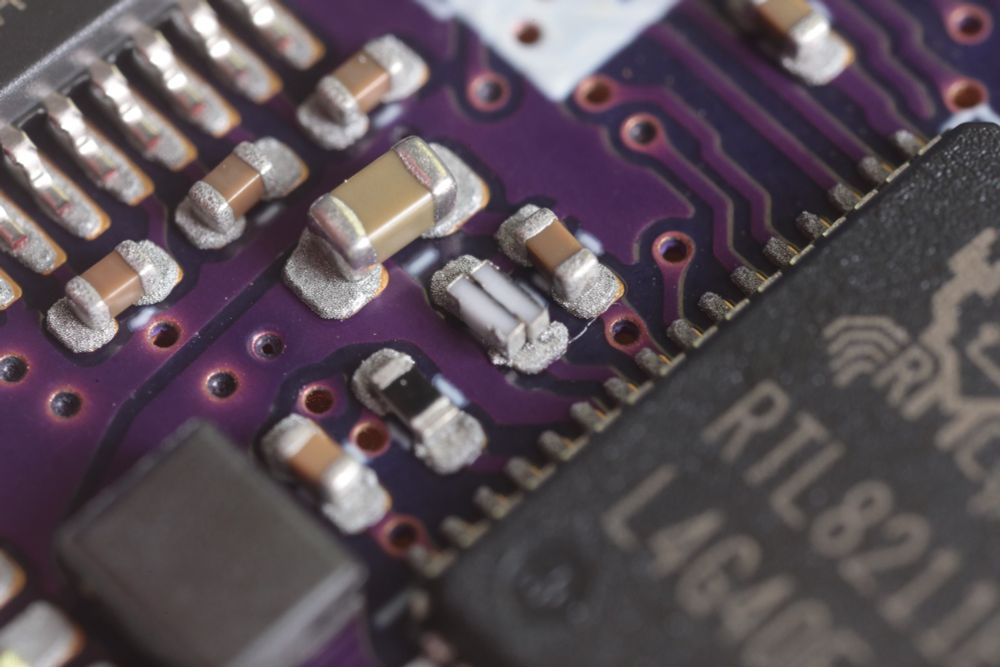

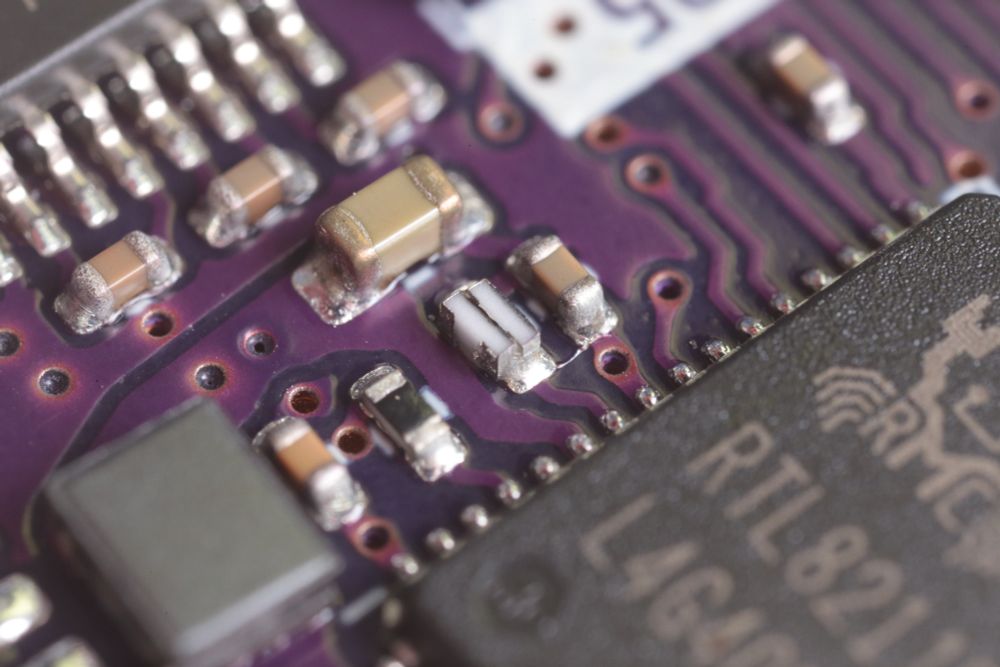

Can't recall where this came from, but ended up in my labs cable drawer. Curious why it wouldn't enumerate.. 🤮

August 14, 2025 at 6:36 AM

Can't recall where this came from, but ended up in my labs cable drawer. Curious why it wouldn't enumerate.. 🤮

Why is my circuit board lying to me 🥲

August 3, 2025 at 7:57 AM

Why is my circuit board lying to me 🥲

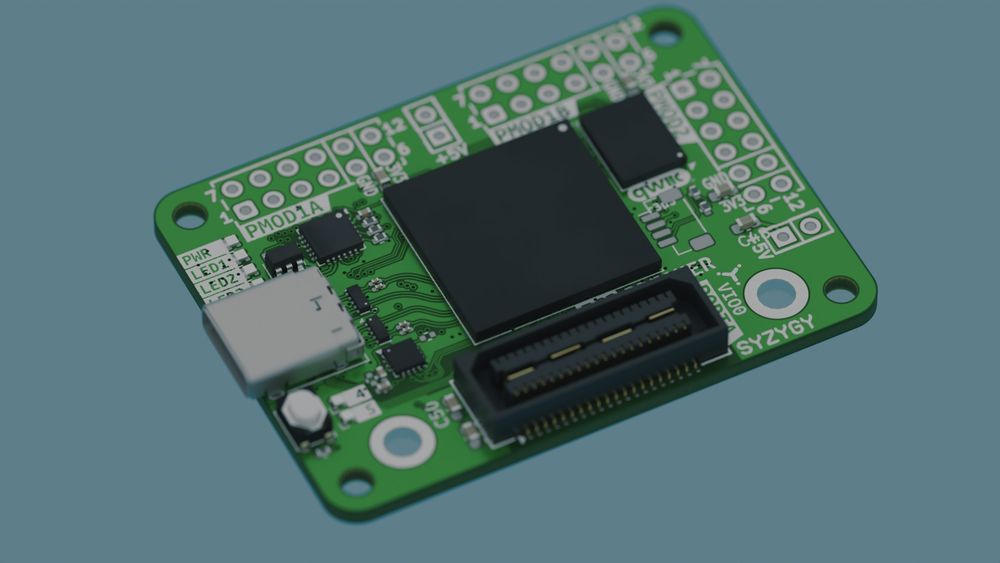

😍 Freshly assembled, still not sure if the design even works 🫣

June 24, 2025 at 3:45 AM

😍 Freshly assembled, still not sure if the design even works 🫣

A nice solder paste application 🫠

June 12, 2025 at 9:13 AM

A nice solder paste application 🫠

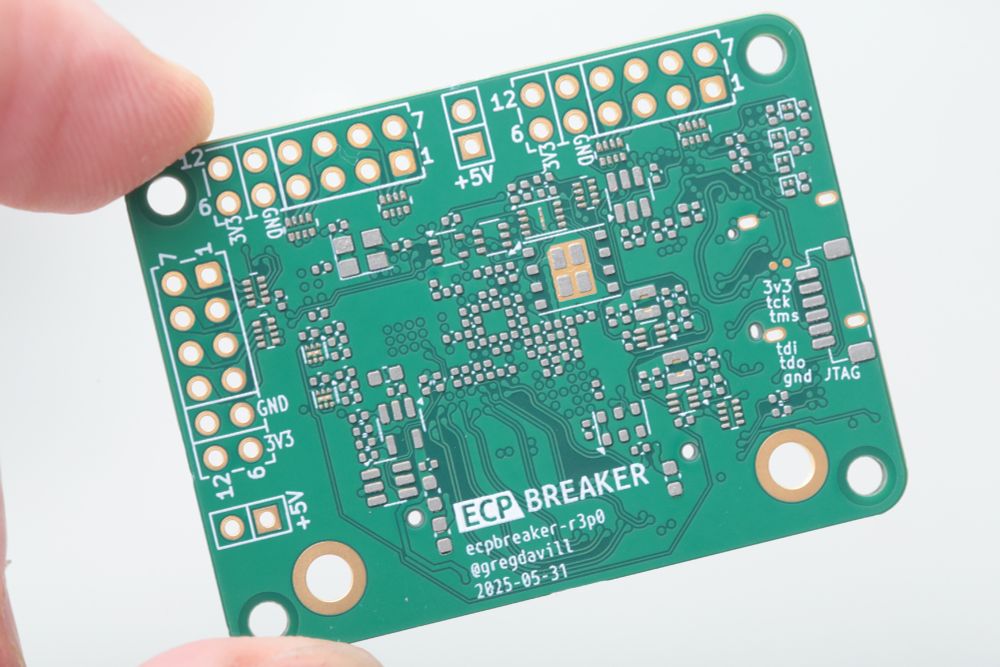

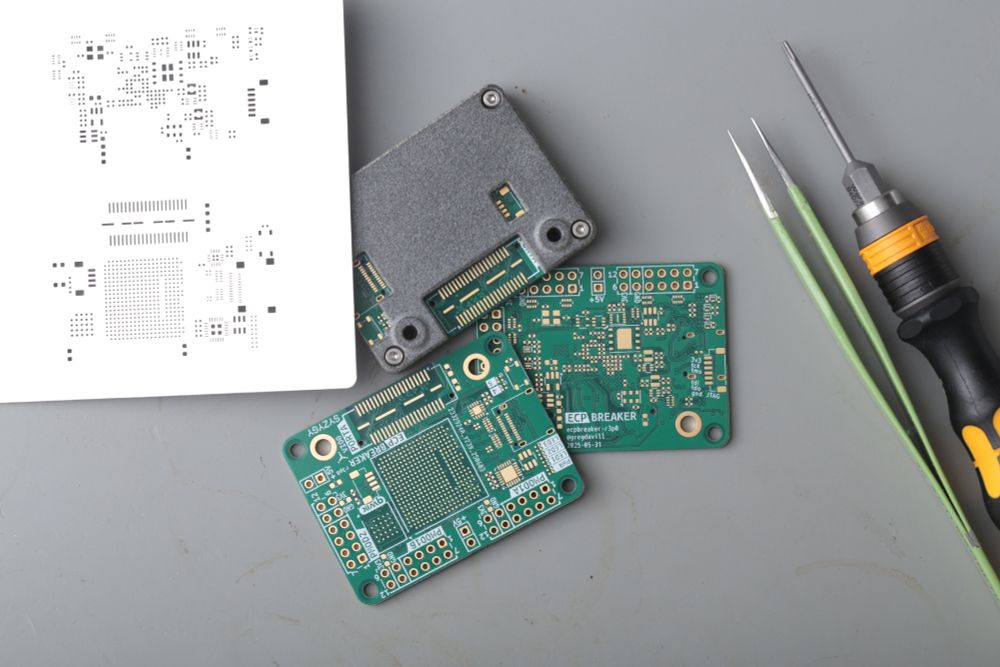

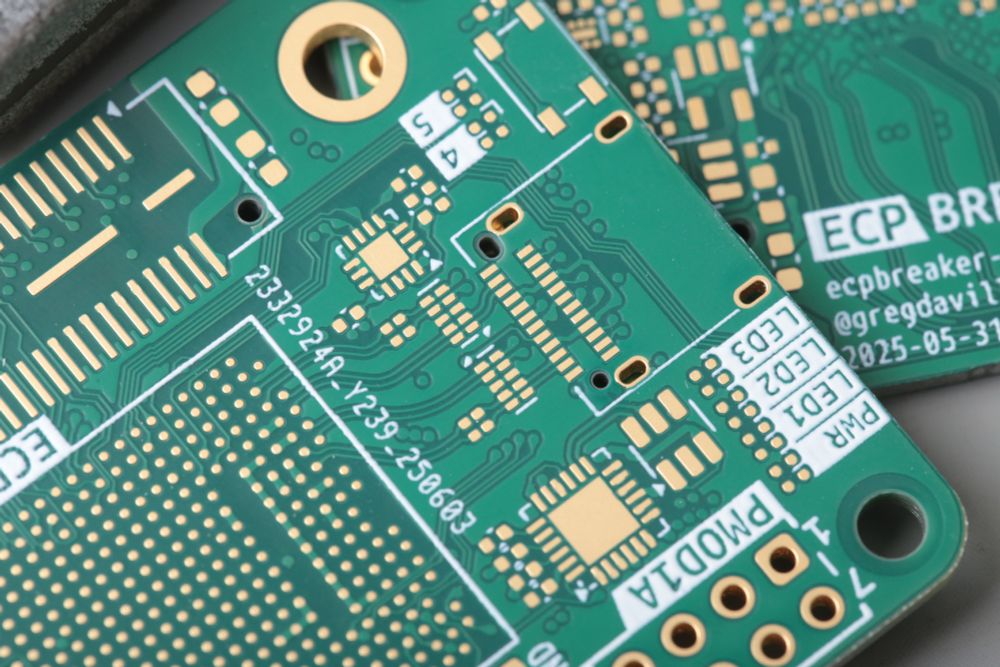

Circuit boards are in! 👌

June 12, 2025 at 1:42 AM

Circuit boards are in! 👌

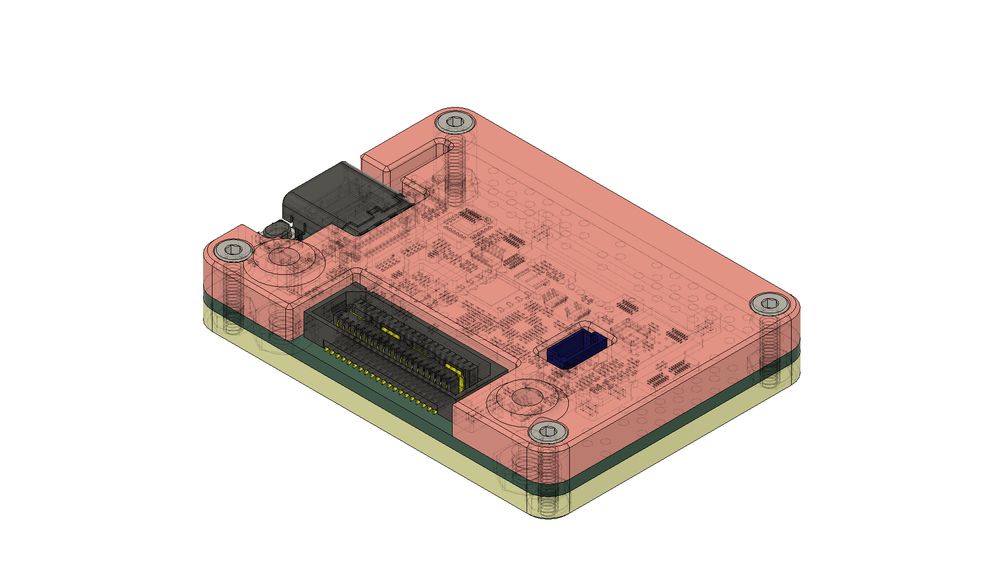

Designed a quick and simple 3d printed case

June 2, 2025 at 10:40 PM

Designed a quick and simple 3d printed case

I've been using KiCad 9's new table features to aid in schematic documentation.

I guess it makes sense.. But still puzzled me for a moment that you can perform a vertical/horizontal mirror on a single cell. 🙃

I guess it makes sense.. But still puzzled me for a moment that you can perform a vertical/horizontal mirror on a single cell. 🙃

May 31, 2025 at 1:50 AM

I've been using KiCad 9's new table features to aid in schematic documentation.

I guess it makes sense.. But still puzzled me for a moment that you can perform a vertical/horizontal mirror on a single cell. 🙃

I guess it makes sense.. But still puzzled me for a moment that you can perform a vertical/horizontal mirror on a single cell. 🙃

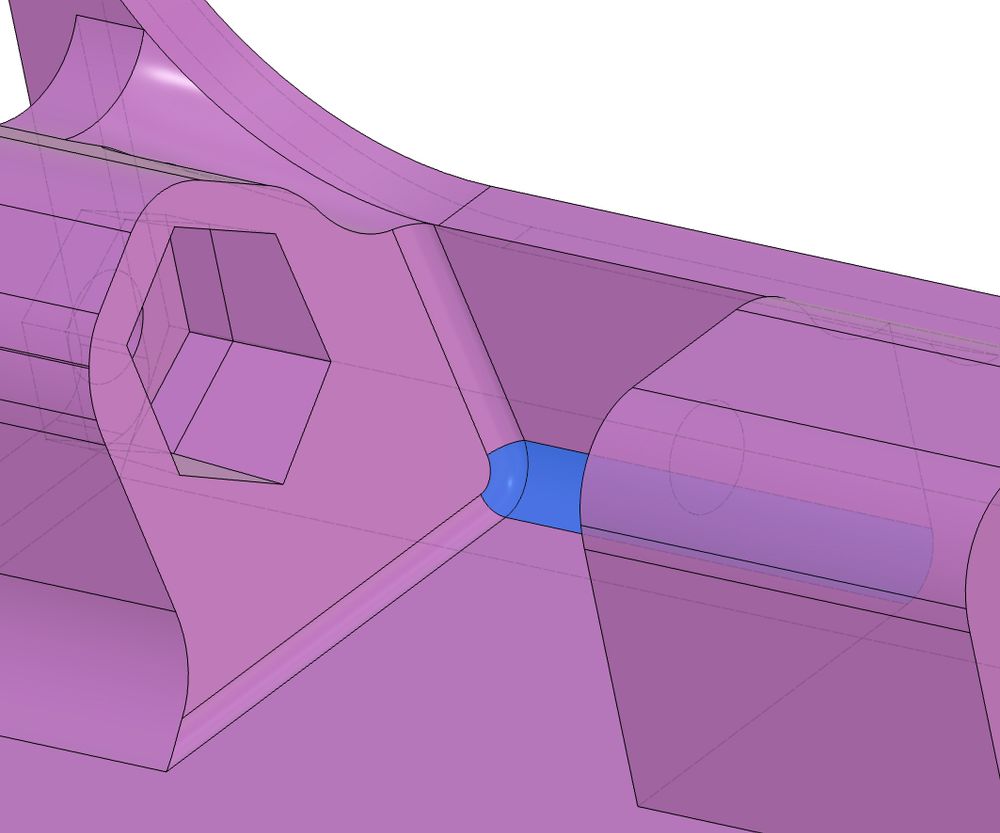

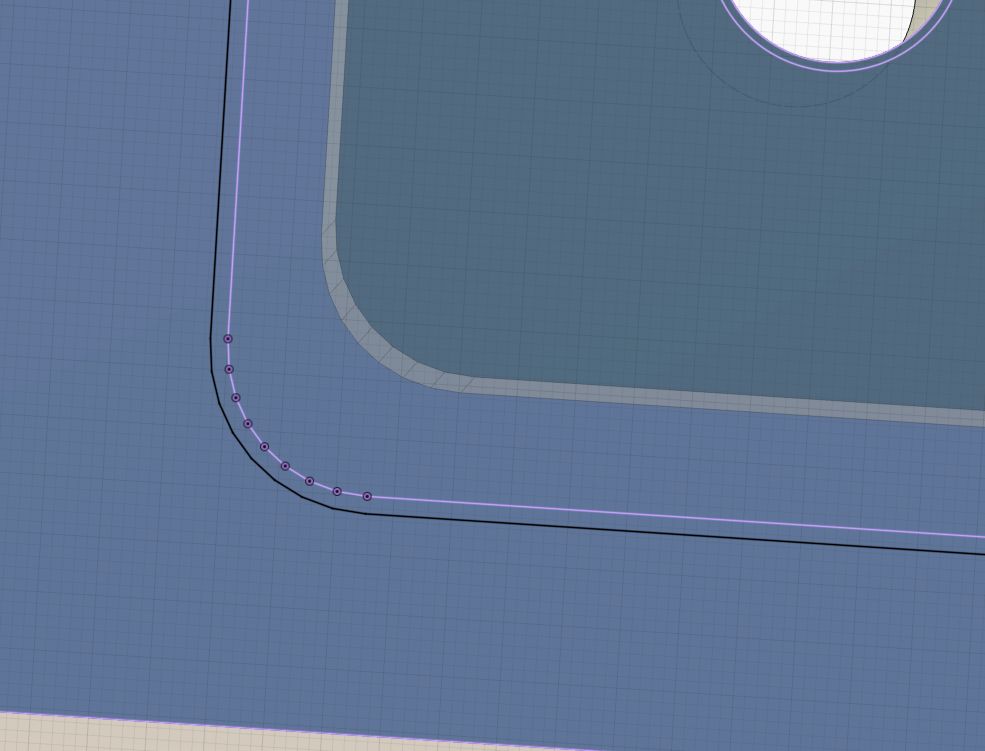

Glad I can jump back in the timeline. Found the culprit!

Top object is an imported PCB, arcs on the board outline get converted to straight-line segments when it's exported from KiCad.

The purple lines are projected from this PCB outline. Then I've applied an offset to account for tolerance.

Top object is an imported PCB, arcs on the board outline get converted to straight-line segments when it's exported from KiCad.

The purple lines are projected from this PCB outline. Then I've applied an offset to account for tolerance.

May 10, 2025 at 6:18 AM

Glad I can jump back in the timeline. Found the culprit!

Top object is an imported PCB, arcs on the board outline get converted to straight-line segments when it's exported from KiCad.

The purple lines are projected from this PCB outline. Then I've applied an offset to account for tolerance.

Top object is an imported PCB, arcs on the board outline get converted to straight-line segments when it's exported from KiCad.

The purple lines are projected from this PCB outline. Then I've applied an offset to account for tolerance.

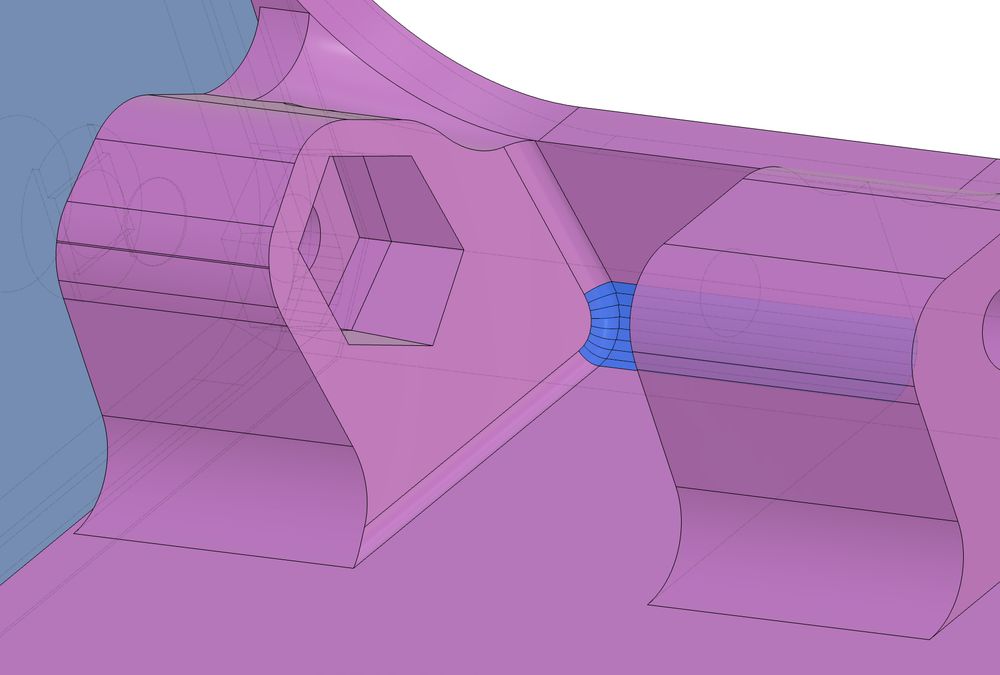

Whoops, it's quick and easy to simply base 3d geometry off a KiCad board outline. But the topology has caught up to me. 🫠

May 10, 2025 at 6:13 AM

Whoops, it's quick and easy to simply base 3d geometry off a KiCad board outline. But the topology has caught up to me. 🫠

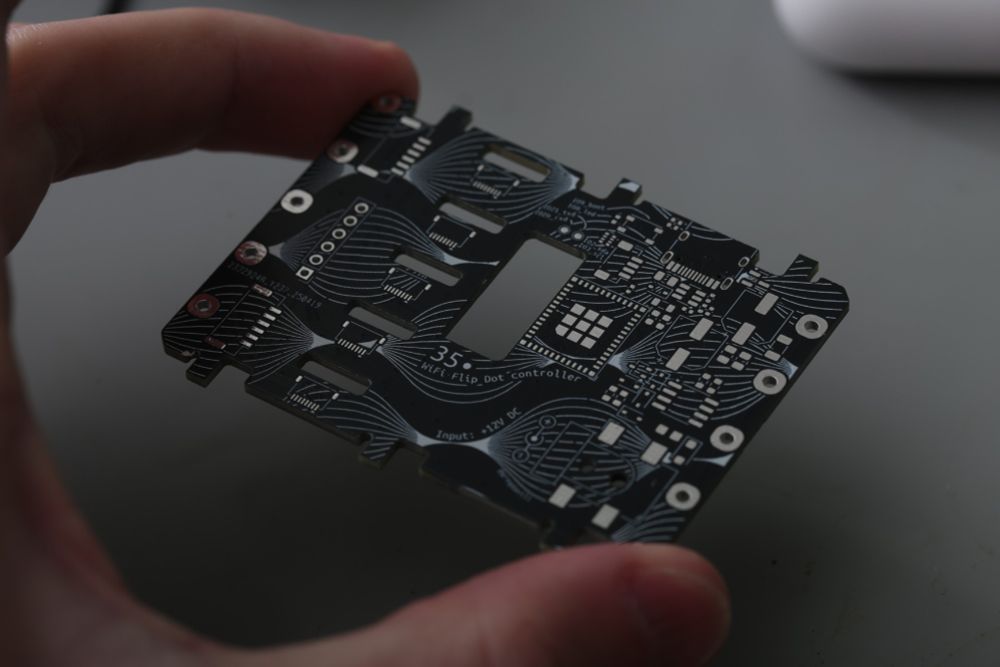

Designed this board years ago, and finally ordered it. The pattern looks really cool on the physical boards.

github.com/gregdavill/a...

github.com/gregdavill/a...

April 30, 2025 at 10:08 AM

Designed this board years ago, and finally ordered it. The pattern looks really cool on the physical boards.

github.com/gregdavill/a...

github.com/gregdavill/a...

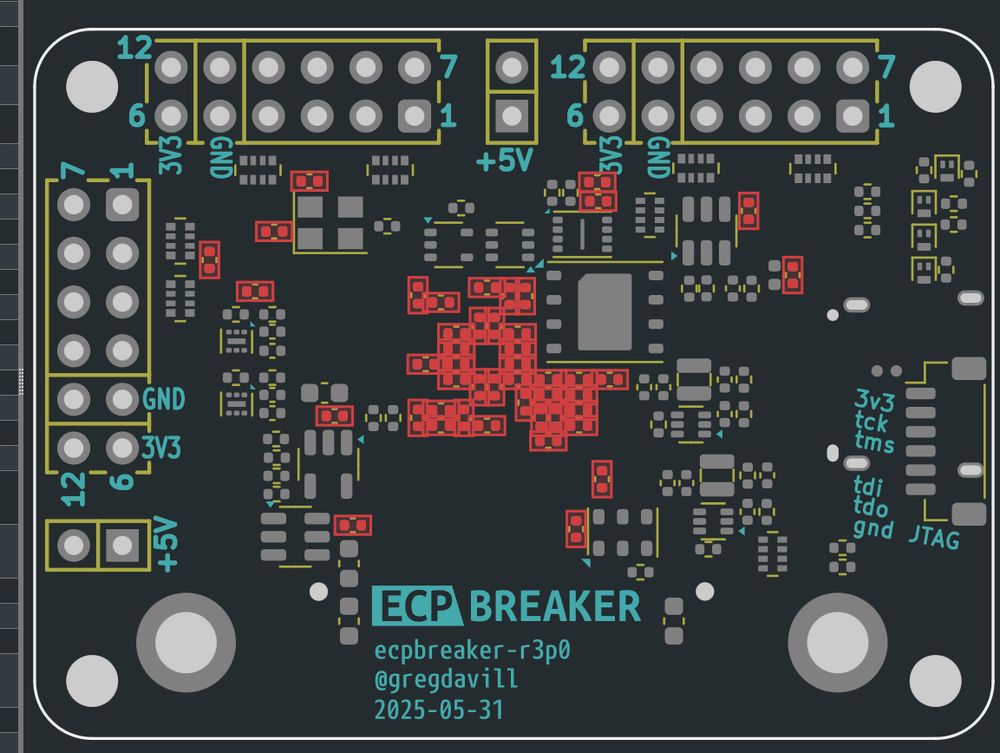

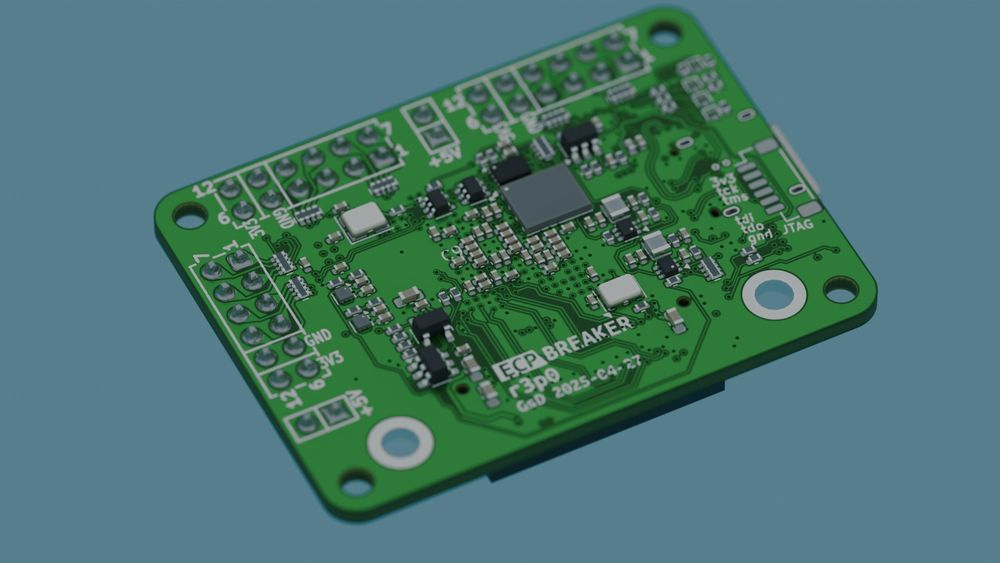

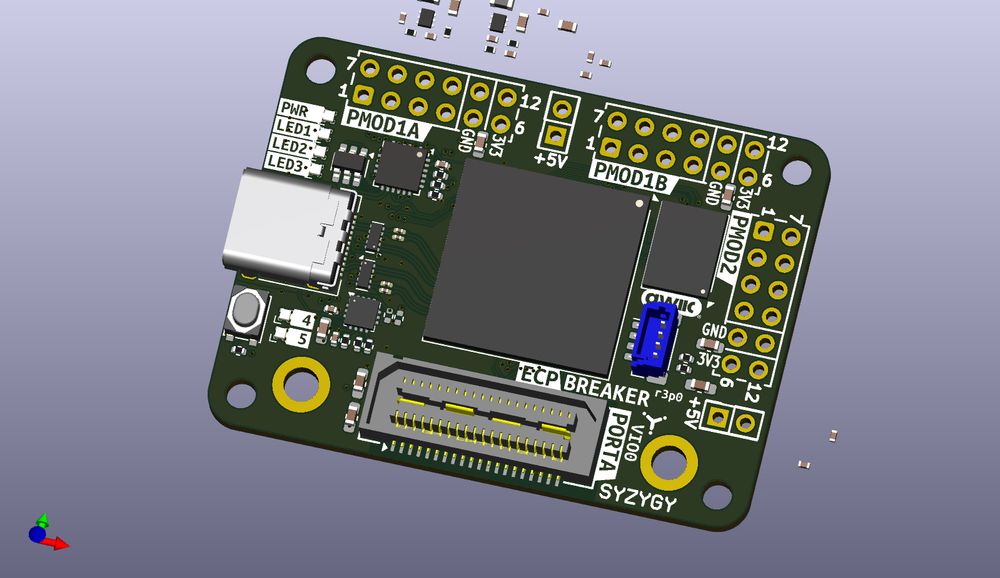

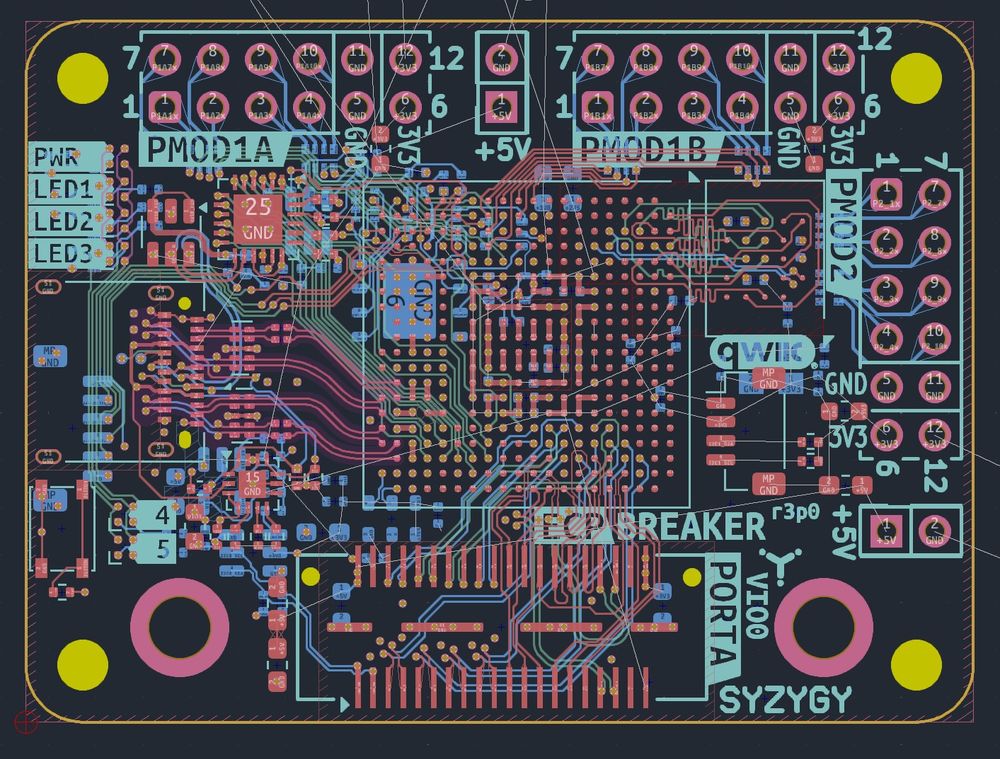

Board is fully routed now, somehow it all fits.

Same sized FPGA as the Butterstick, but on a board less than half the size

Same sized FPGA as the Butterstick, but on a board less than half the size

April 27, 2025 at 6:17 AM

Board is fully routed now, somehow it all fits.

Same sized FPGA as the Butterstick, but on a board less than half the size

Same sized FPGA as the Butterstick, but on a board less than half the size

Had an idea, and I nerd-sniped myself into building it...

Similar idea to the last ecpbreaker design, but adding the 5Gbps SERDES to enable USB3. The ECP5's serdes supports display-port, so you could probably do some cool alt-mode stuff, but currently only routed for SS USB.

Similar idea to the last ecpbreaker design, but adding the 5Gbps SERDES to enable USB3. The ECP5's serdes supports display-port, so you could probably do some cool alt-mode stuff, but currently only routed for SS USB.

April 23, 2025 at 12:54 PM

Had an idea, and I nerd-sniped myself into building it...

Similar idea to the last ecpbreaker design, but adding the 5Gbps SERDES to enable USB3. The ECP5's serdes supports display-port, so you could probably do some cool alt-mode stuff, but currently only routed for SS USB.

Similar idea to the last ecpbreaker design, but adding the 5Gbps SERDES to enable USB3. The ECP5's serdes supports display-port, so you could probably do some cool alt-mode stuff, but currently only routed for SS USB.

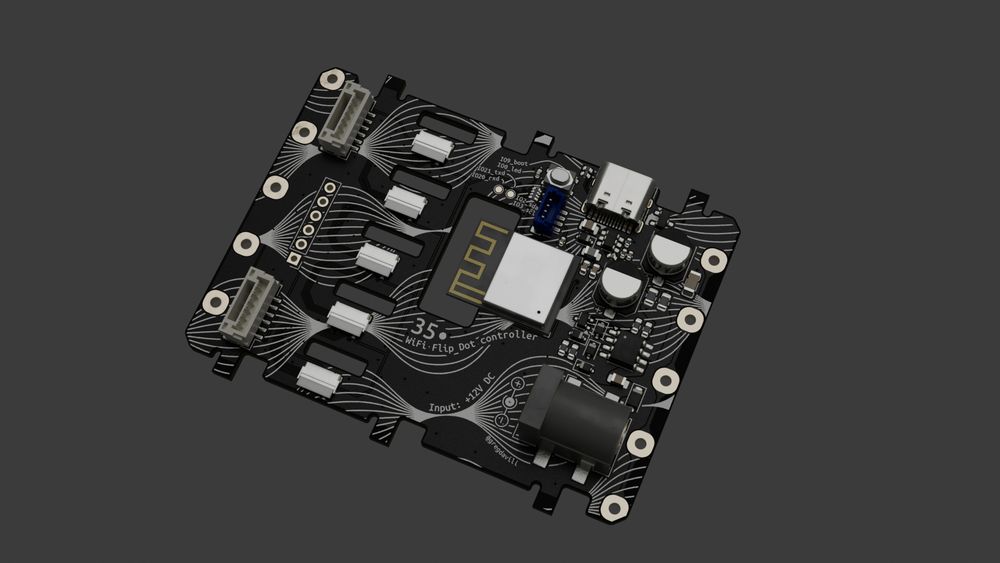

Spun up a new design to add an ESP32-C3 module to the back of the flip-dot module, along with DC power input.

Got a little carried away in inkscape for the silkscreen.

Trying out github.com/30350n/pcb2b..., a plugin that is in the KiCad PCM for exporting textures directly into blender, works great

Got a little carried away in inkscape for the silkscreen.

Trying out github.com/30350n/pcb2b..., a plugin that is in the KiCad PCM for exporting textures directly into blender, works great

April 21, 2025 at 4:30 AM

Spun up a new design to add an ESP32-C3 module to the back of the flip-dot module, along with DC power input.

Got a little carried away in inkscape for the silkscreen.

Trying out github.com/30350n/pcb2b..., a plugin that is in the KiCad PCM for exporting textures directly into blender, works great

Got a little carried away in inkscape for the silkscreen.

Trying out github.com/30350n/pcb2b..., a plugin that is in the KiCad PCM for exporting textures directly into blender, works great

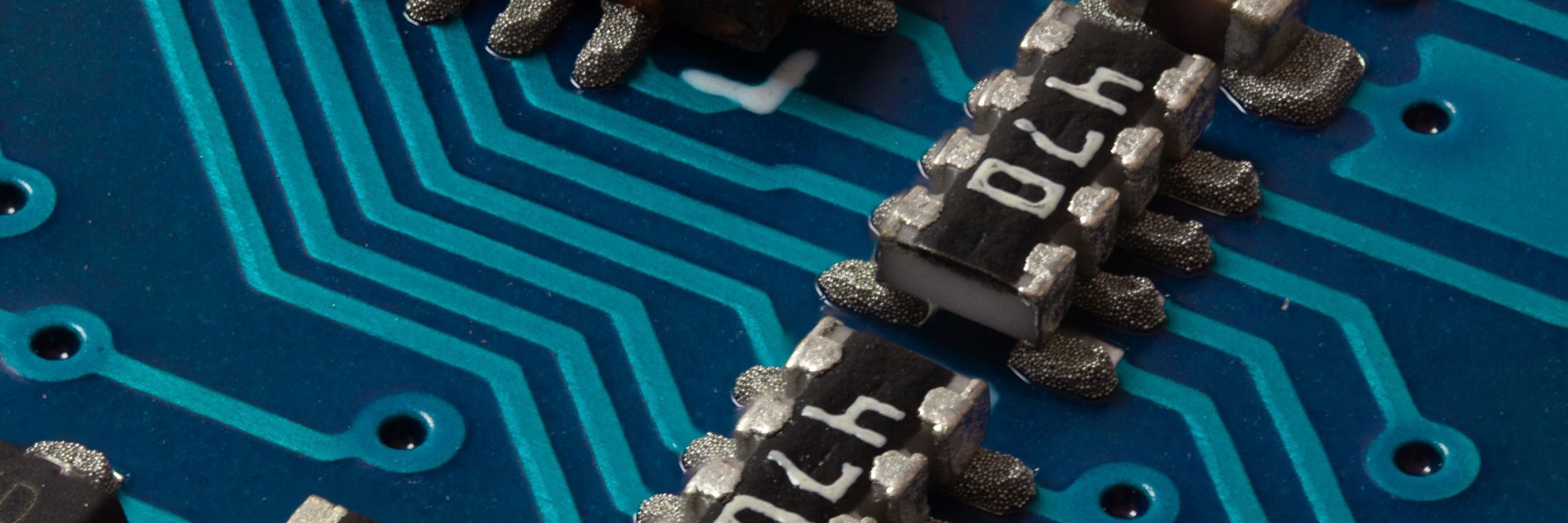

When you don't have the exact part... Just place a parallel combination 🙃

April 5, 2025 at 10:09 AM

When you don't have the exact part... Just place a parallel combination 🙃