Queer Kinky Poly Mess 🏳️🌈 🏳️⚧️

CTO @YosysHQ 😺 RISC-V, SMT 👩💻

Opinions are my Ceti eel's 😛

ACAB BLM ✊ I am Antifa 🏴🚩

Vienna, Austria 📌 she/her 🧚♀️

![Slide from Hot Chips 2025:

"2025 TCMM Open Source Hardware Contribution Award:

Claire Wolf: In recognition of outstanding contributions to RISC-V —

including BitManip, RVFI, and PicoRV32—and to open-source tools like Yosys and IceStorm. [IEEE Computer Society TCMM / Technical Community on Microprocessors and Microcomputers]"](https://cdn.bsky.app/img/feed_thumbnail/plain/did:plc:egm6nnyusca4icjiqlb7pyiw/bafkreidgommoceirpkrigeshonoc5zmyhj2dnipsi5wngbl72z64ep3jze@jpeg)

Please consider including SAG/inverse-SAG with bit-reversal of the goats.

No matter which of the two implementation methods you are using: All you need to do is not mask the goat bits.

Please consider including SAG/inverse-SAG with bit-reversal of the goats.

No matter which of the two implementation methods you are using: All you need to do is not mask the goat bits.

github.com/clairexen/ed...

I can't see any obvious reason why that identity should not extend beyond 8-bit units. But I have not actually tested that hypothesis yet.

github.com/clairexen/ed...

I can't see any obvious reason why that identity should not extend beyond 8-bit units. But I have not actually tested that hypothesis yet.

I can’t say if the storm is fate or man-made.

I only know I’m losing light.

I can’t say if the storm is fate or man-made.

I only know I’m losing light.

I just wrote this:

github.com/clairexen/ed...

I've been meaning to write this code for quite some time...

I just wrote this:

github.com/clairexen/ed...

I've been meaning to write this code for quite some time...

described in arxiv.org/abs/2405.12949 (that just got accepted pending minor revisions)

described in arxiv.org/abs/2405.12949 (that just got accepted pending minor revisions)

youtu.be/wM4cobfjMMQ

Don't miss the Black Friday discounts - join the newsletter for $150 off on Friday: zerotoasiccourse.com/newsletter/

Full course details: zerotoasiccourse.com/analog/

youtu.be/wM4cobfjMMQ

Don't miss the Black Friday discounts - join the newsletter for $150 off on Friday: zerotoasiccourse.com/newsletter/

Full course details: zerotoasiccourse.com/analog/

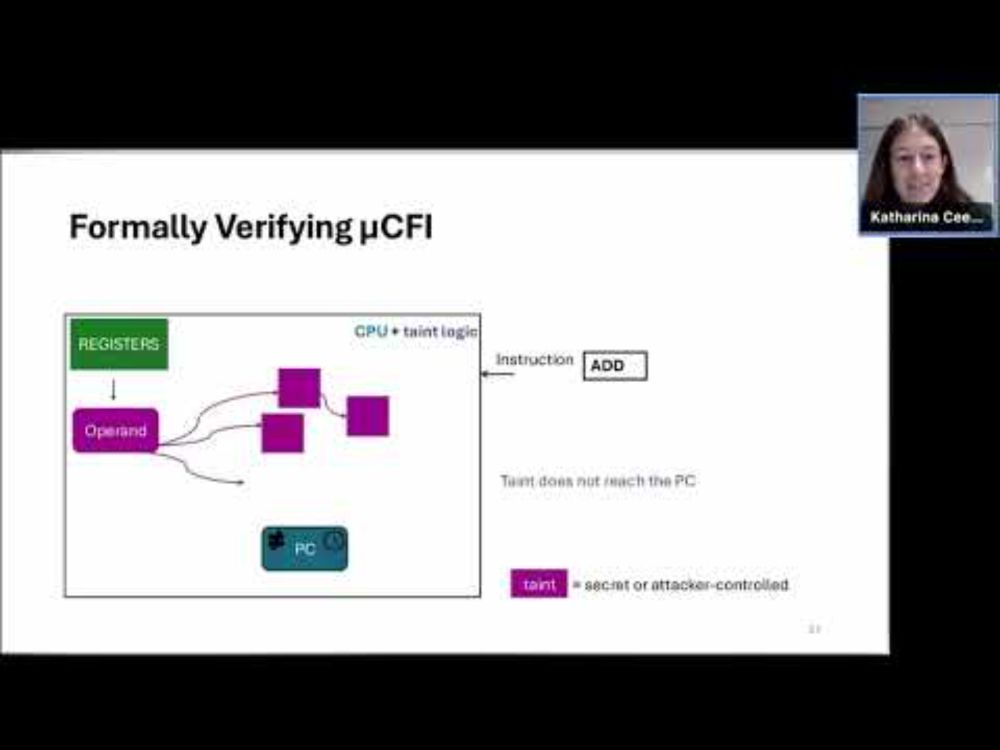

In our last call, Katharina CeesaySeitz from ETH Zürich presented her work to detect microarchitectural information leakage via hardware timing side channels.

Watch her talk on our Youtube channel!

www.youtube.com/watch?v=Kxp-...

In our last call, Katharina CeesaySeitz from ETH Zürich presented her work to detect microarchitectural information leakage via hardware timing side channels.

Watch her talk on our Youtube channel!

www.youtube.com/watch?v=Kxp-...

fpgacpu.ca/fpga/handsha...

fpgacpu.ca/fpga/handsha...

⬜🟨🟨⬜⬜

🟨🟩🟩🟨🟩

🟩🟩🟩🟩🟩

ROFL 🤣

⬜🟨🟨⬜⬜

🟨🟩🟩🟨🟩

🟩🟩🟩🟩🟩

ROFL 🤣

⬜⬜🟨⬜🟩

🟩🟩🟩🟩🟩

⬜⬜🟨⬜🟩

🟩🟩🟩🟩🟩

This picture makes a lot of sense ;)

This picture makes a lot of sense ;)

it's all the same math, just rearranged

it's all the same math, just rearranged